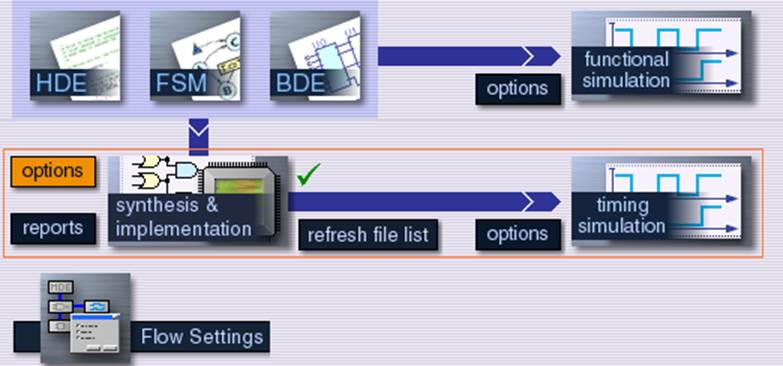

2.2. После закрытия панели FlowConfigurationSettings на закладке designflow manager появятся новые кнопки, связанные с процедурами синтеза, реализации и временного моделирования. На рис.4 они обведены прямоугольником красного цвета.

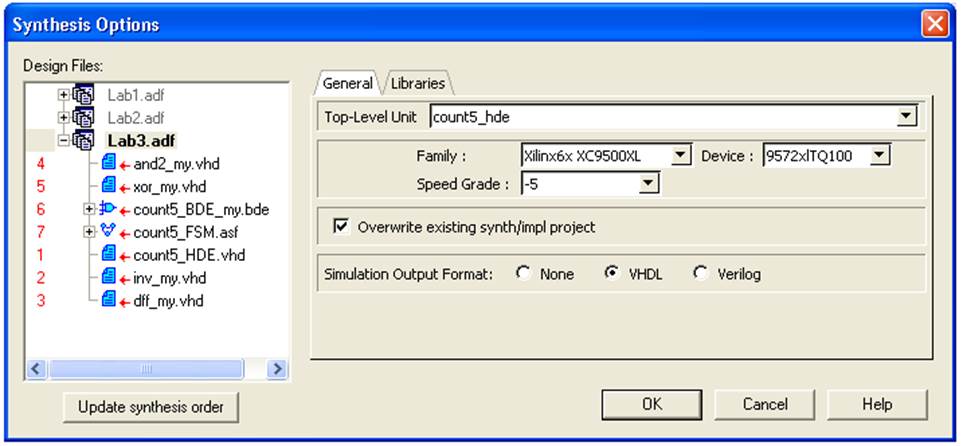

Щёлкните по кнопке ![]() слева от пиктограммы synthesis

& implementation. Откроется диалоговая панель SynthesisOptions (рис.5), на которой надо выбрать в раскрывающемся

списке Top-LevelUnit имя

модуля верхнего уровня (например, count5_HDE),

в списке Family - семейство

ПЛИС (Xilinx6xXC9500XL),

а в списке Device - имя целевой микросхемы (9572xlTQ100).

слева от пиктограммы synthesis

& implementation. Откроется диалоговая панель SynthesisOptions (рис.5), на которой надо выбрать в раскрывающемся

списке Top-LevelUnit имя

модуля верхнего уровня (например, count5_HDE),

в списке Family - семейство

ПЛИС (Xilinx6xXC9500XL),

а в списке Device - имя целевой микросхемы (9572xlTQ100).

Рис.4. На закладке управления потоком проектирования DesignFlowManager

появился новый маршрут: синтез, реализация и временное моделирование

(выделено красным цветом)

В левом окне DesignFiles можно исключить из списка ненужные для синтеза модули, а при необходимости включить их снова.

Рис.5. На диалоговой панели SynthesisOptions устанавливаем желаемые опции синтеза

По умолчанию в поле SpeedGrade задаётся самый высокий уровень быстродействия «-5». В дальнейшем вам предстоит провести несколько экспериментов с различными значениями этого параметра.

2.3. На закладке design flow manager (см. рис.4) щёлкните по иконке синтез и реализация.

В результате этого действия из интегрированной среды проектирования Active-HDL 7.1 автоматически запустится другая САПР XilinxISE 6.2, в которой и будут выполняться названные процедуры.

Если вы увидите чужой проект, то закройте его (команда File/CloseProject) и откройте свой (команда File/OpenProject).

Проект имеет расширение *.npl и должен находиться в директории synthesis, которая в свою очередь вложена в папку с названием вашего проекта (например, Lab3).

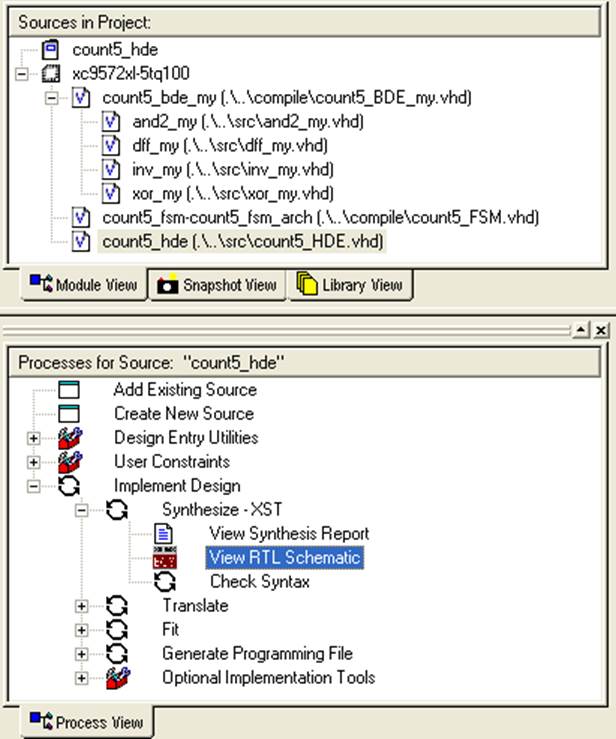

2.4. На открывшейся диалоговой панели САПР XilinxISE в окне SourcesinProjectвыделите желаемый вариант описания проекта для синтеза, например count5_hde (рис. 6). В принципе вы можете синтезировать любую часть своего проекта, которая видна в окне SourcesinProject, например dff_my или and2_my. В данном случае – это элементы структурного описания проекта.

Рис.6. Основные окна управляющей оболочки Навигатора Проекта в САПР XilinxISE 6.2

В нижнем окне ProcessesforSource вы увидите дерево процедур (процессов), доступных для выделенного в верхнем окне модуля.

Активизируйте процесс ViewRTLSchematic. Он находится в ветви ImplementDesign (реализация проекта) и вложен в процедуру Synthesize – XST(XilinxSynthesisTechnology).

При этом будут выполнены все предшествующие процедуры, которые оказывают влияние на исполняемый процесс. В данном случае будет выполнен синтез вашего проекта на RTL – уровне, а его результаты в виде функциональной схемы выведены в окне графического редактора ECS – EngineeringCaptureSystem.

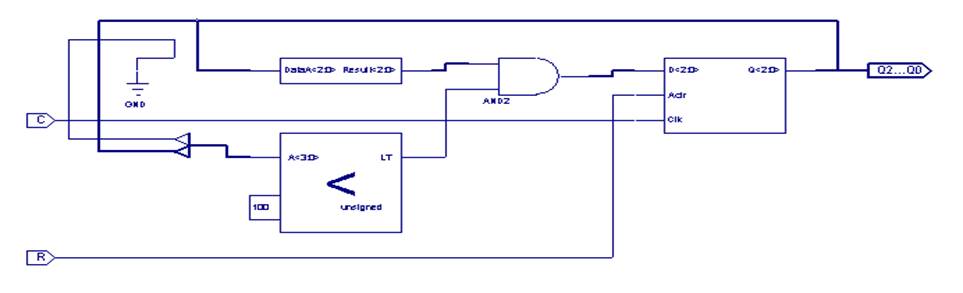

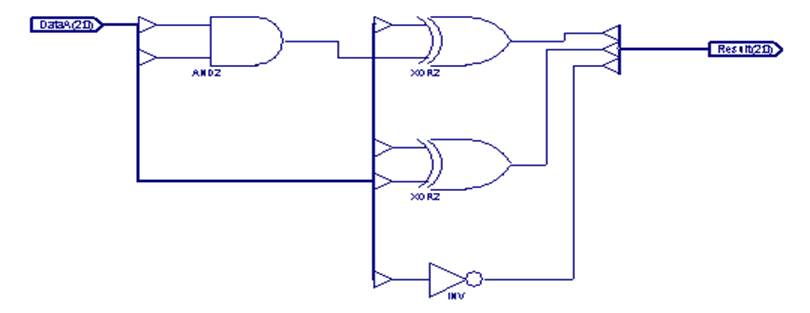

Для рассматриваемого примера count5_hde будет синтезирована схема, показанная на рис.7 (вариант VHDL - модели).

Схема является иерархической и отдельные её модули можно раскрыть, если дважды щёлкнуть на любом из них левой кнопкой мыши (рис.7,б). Для повышения уровня иерархии курсор мыши следует поместить на свободном месте рисунка и вновь дважды щёлкнуть мышью. Иерархия может быть многоуровневой.

а)

а)

б)

Рис.7. Функциональная схема счётчика по модулю 5,

полученная в результате синтеза

в САПР XilinxISE 6.2. На рис 7,б в качестве примера раскрыт один из

её фрагментов

2.5. Выделите в окне SourcesinProject второй вариант описания вашего проекта (в виде цифрового автомата) и повторите описанную выше процедуру синтеза. По умолчанию система автоматически выбирает наиболее экономичное внутреннее кодирование регистра состояния. Как правило – это бинарное кодирование, для которого требуется минимальное число триггеров.

Поэтому проделайте ещё один эксперимент, задав иной способ кодирования состояний, например One-Hot (1 из N). Для этого щёлкните правой кнопкой мыши на строке SynthesizeXST (см. рис.6) и исполните в контекстном меню команду Properties.

Откроется диалоговая панель ProcessProperties с тремя закладками. Активизируйте закладку HDLOptions и для параметра FSMEncodingAlgorithm установите значение One-Hot. Вновь запустите процедуру ViewRTLSchematic. Оцените влияние способа кодирования внутренних состояний на объём получаемой схемы и, прежде всего, на требуемое число триггеров в регистре состояния (особенно наглядно влияние алгоритма кодирования проявляется при потоковом описании цифрового автомата).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.