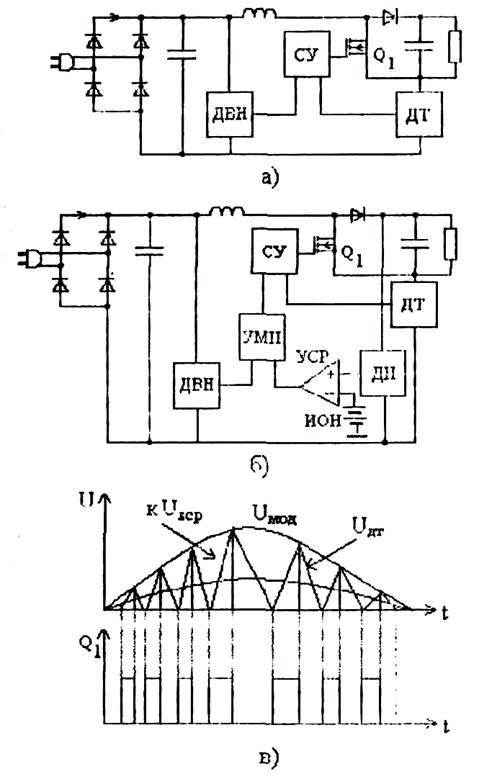

Рис.3. Принцип работы активных корректоров коэффициента мощности

|

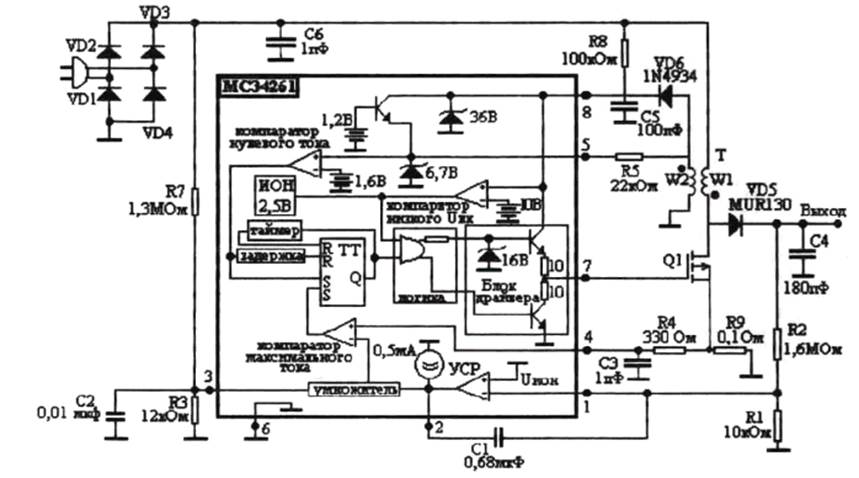

Рис. 4. Корректор на 175 Вт с микросхемой МС34261

Принципиальная схема корректора мощности на 175 Вт, с использованием микросхемы МС33261 в качестве СУ, представлена на рис. 4.

Такие блоки, как драйвер, триггер-защелка, датчик тока реактора, усилитель сигнала рассогласования в обратной связи по напряжению, блоки защиты, являются обычными для СУ импульсными регуляторами и не претерпели по сравнению с UC3842 существенных изменений. В этих неспецифических блоках, содержащихся и в структуре СУ корректорами, используются все последние достижения фирмы в разработке СУ импульсными стабилизаторами.

Для получения СУ корректоров эта микросхема дополнена умножителем напряжений и, кроме того, генератор постоянной частоты заменен компаратором нулевого тока. Кратко рассмотрим назначение основных блоков, приведенных на рис. 4, начав с общим для всех приведенных микросхем.

Блок драйвера - выходной блок СУ, обеспечивающий управление силовым транзистором импульсного регулятора.

Блок триггера - защелки ( ТТ ) определяет момент отпирания и запирания силового транзистора. При идеальных характеристиках компараторов моменты переключения определялись бы непосредственно состоянием их выходов и необходимости в этом блоке не было. Однако, в моменты переключения, компараторы работают в линейном режиме при малых входных сигналах, и возникает проблема их многократного переключения под действием помех (известное явление "дребезга", вызывающее неоправданные потери мощности в импульсном регуляторе). Введение в структуру триггера - защелки устраняет этот недостаток, поскольку вход триггера становится нечувствительным к помехам сразу же после очень короткого интервала переключения.

Логический блок вырабатывает импульс запрета сигналу, отпирающему силовой транзистор, при срабатывании различных защитных блоков, но не может запереть уже открытый транзистор. Поэтому он используется для реализации относительно инерционных цепей защиты. В данной микросхеме функцию логического блока, реализующего запрет от блока защиты при пониженном напряжении питания, выполняет двухвходовая схема И.

Компаратор максимального тока определяет момент выключения силового транзистора. На один из его входов подается сигнал с датчика тока в индуктивности, на другой - с умножителя.

Усилитель сигнала рассогласования ( УСР ) выполняет обычные функции обратной связи по выходному напряжению.

Источник опорного напряжения ( ИОН ) вырабатывает внутренние опорные сигналы на всех компараторах и имеет, по крайней мере, один вывод опорного напряжения для внешних цепей.

Блок защиты от пониженного напряжения питания обеспечивает отключения корректора при низком входном напряжении, приводящем в отсутствии такой защиты увеличению среднего значения входного тока и к соответствующему увеличению потерь и температуры в силовом транзисторе и реакторе (или трансформаторе, если он имеется в схеме).

Среди блоков СУ корректорами мощности имеются три обязательных, присутствующих во всех СУ: умножитель, компаратор нулевого тока и таймер.

Умножитель определяет момент выключения силового транзистора. Функция этого блока - основная для СУ корректорами.

Компаратор нулевого тока определяет в СУ корректорами момент включения силового транзистора.

Таймер дублирует импульс запуска при сбоях компаратора нулевого тока, при начальном и повторном запусках. Поскольку компаратор нулевого тока выдает один импульс в момент достижения нулевого тока, любой случайный сбой в отпирании силового транзистора может привести к срыву работы. Для предотвращения этого импульса запуска дублируется импульсом таймера - одновибратора, запускаемого в момент срабатывания компаратора. В стандартном рабочем режиме отпирающий импульс таймера запаздывает относительно импульса, формируемого триггером, и не влияет на работу схемы, но в нестандартных ситуациях он отпирает силовой транзистор.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.