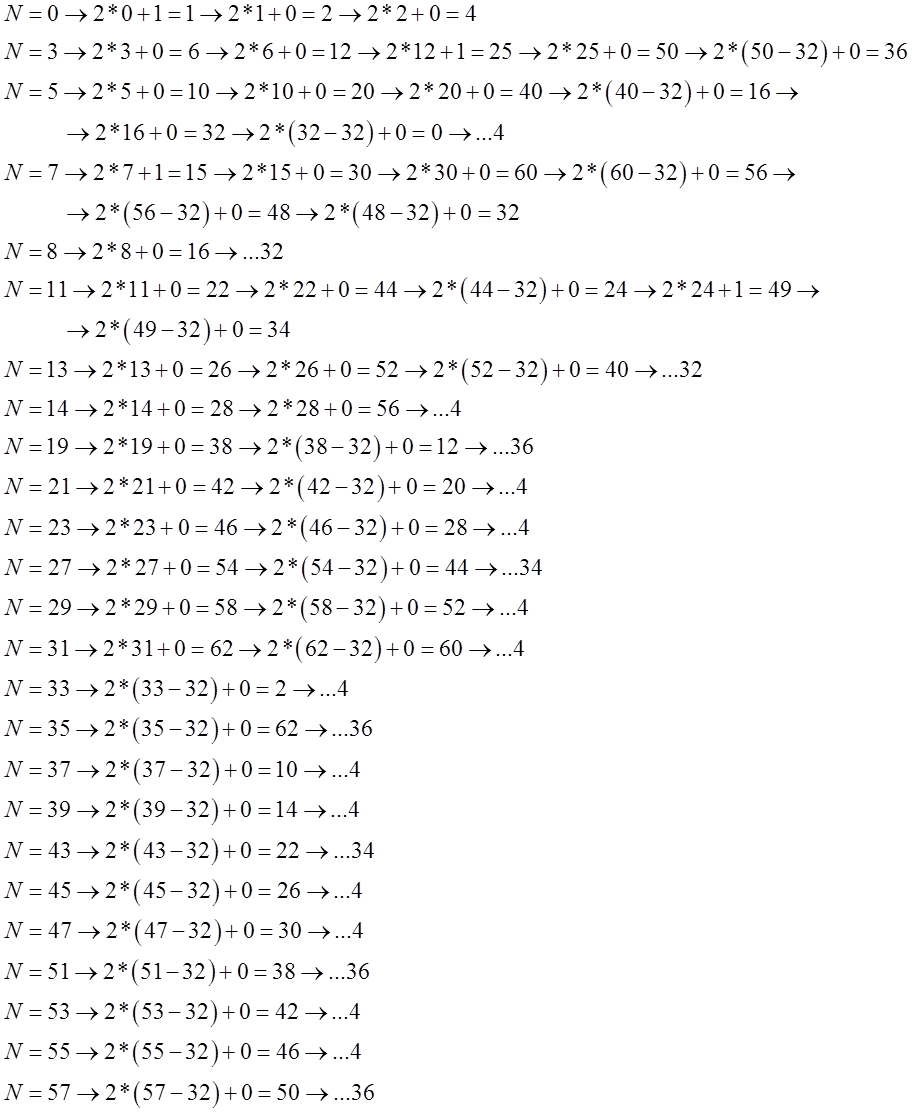

Виходимо з того, що парні коди N = Q2Q1Q0 закінчуються на 0, а непарні – на 1, тому в клітинку діаграми з номером N вписуємо значення Q0+ = 0, якщо наступний код робочого циклу є парний, і Q0+ = 1, якщо непарний. 3.2 Аналіз функціонування пристрою, його самовідновність та повний перемикальний граф. Принципова схема ЦПП, часові діаграми перемикання з позначенням затримок. Перед тим як скласти принципову схему, потрібно перевірити пристрій на самовідновність. З цією метою виконаємо наступні розрахунки:

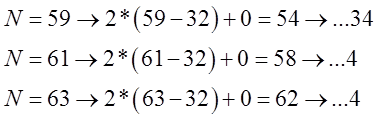

Повний перемикальний граф буде мати такий вигляд:

Рисунок 3.2 - Перемикальний граф

З перемикального графу видно, що пристрій є самовідновним. Реверсивний генератор кодової послідовності ми отримуємо при заміні виходів Q0, Q1, Q2, Q3, Q4, Q5 на відповідно: Q5, Q4, Q3, Q2, Q1, Q0

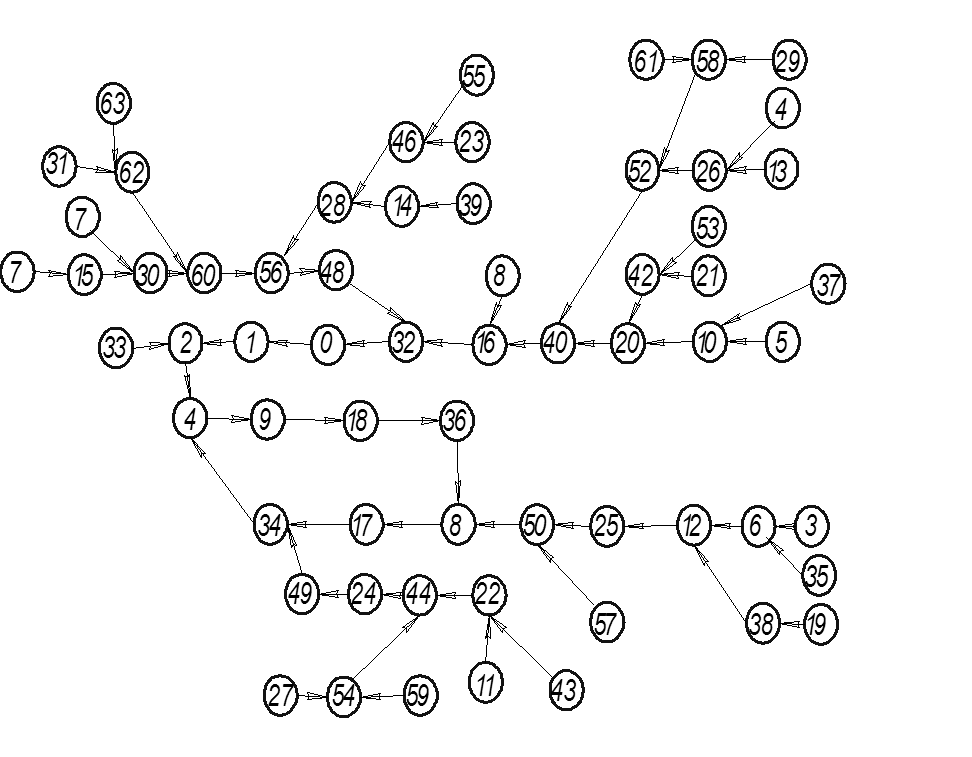

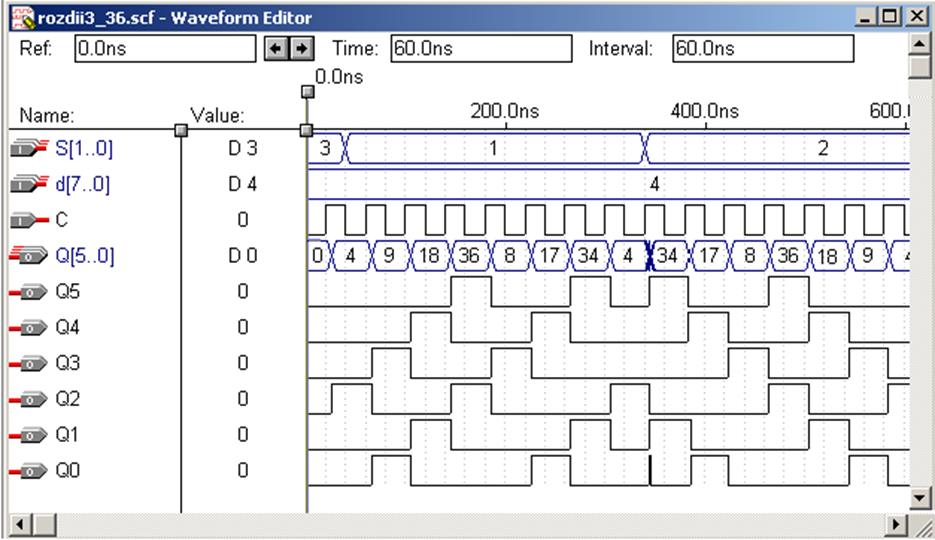

Нижче наведено часові діаграми перемикання розроблюваного пристрою.

Рисунок 3.3 - Часові діаграми перемикання

3.3 Елементи технічного проектування

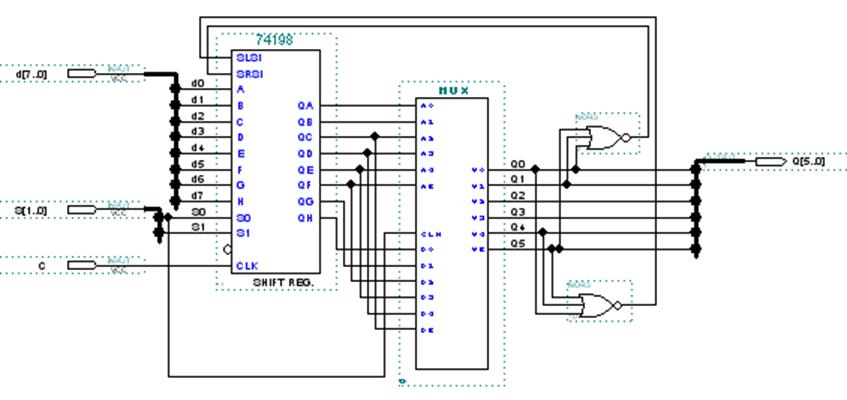

Для реалізації отриманого в результаті вище наведених розрахунків генератора я вибрав 1 інтегральну схему серії 4CY74198N (реверсивний регістр зсуву), інтегральну схему серії 5427FM (з трьома елементами АБО-НЕ), інтегральну схему серії 54151FM (восьми розрядний мультиплексор .

Схема елементів технічного проектування наведенана в додатках (Додаток А).

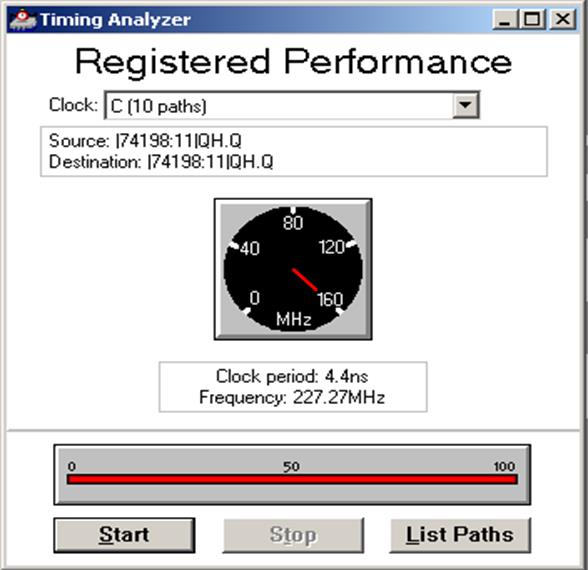

Максимальна частота вхідних імпульсів буде визначатись елементом, у якого найменша максимальна частота:

Fmax =15 МГц.

Тривалість імпульсів вибираємо такими, щоб усі елементи могли переключитись у необхідний стан:

ti = 150 нс

Напруга живлення:

Еж =5.2 В

Логічні рівні напруги для “0” та “1” відповідно:

Е0 =0.22 В

Е1 =0,75 В

Споживаний струм: Iспож= 6 мА

3.4 Аналіз спроектованого пристрою на ЕОМ. На рисунку 3.4 зображено схему пристрою, якою я користувався для його аналізу в пакеті MAX+plus II

Рисунок 3.4 - Схема аналізу пристрою в пакеті MAX+plus II

Результати аналізу приведені на рисунках 3.5-3.6.

Рисунок 3.5 - Часова діаграма ГКП

Рисунок 3.5 – Результат автоматичного аналізу швидкодії за допомогою дисплея Registered Performance

Так як дані попередніх розрахунків та моделювання збігаються, то пристрій спроектовано вірно.

Креслення по ДСТУ розробленого пристрою наведені на рисунку 3.6.

Висновок

В результаті виконання курсової роботи проведено алгебраїчне додавання заданих десяткових чисел з застосуванням різних кодів, переведення чисел з одних систем до інших.

У першій частині курсової роботи було розглянуто роботу з числами у різних системах числення, а саме, перехід з однієї систему в іншу та математичні операції з числами.

У другій частині курсової роботи було розглянуто різні методи спрощення заданої функції: за допомогою формул алгебри логіки, з використанням діаграм термів, редукції. При цьому отриману мінімальну функцію було реалізовано на інтегральних схемах вибраної серії.

У третій частині курсової роботи було спроектовано подільник частоти послідовний безвентильний, а також виконані елементи технічного проектування, відповідно до вибраних інтегральних схем конкретної серії.

Список використаної літератури

1. Зубчук В.І. , Сигорський В.П., Шкуро А.Н. – Справочник по цифровой схемотехнике. – Киев: Техника, 1990.

2.Пресухин Л.Н.,Воробьев Н.В., Шишкевич А.А. – Расчет элементов цифровых устройств.

3. Шило В.Л. – Популярные цифровые микросхемы :Справочник. – Москва :Радио и связь, 1989.

4. Шабалин Р.В. – Цифровые КМОП микросхемы: Справочник. – Свердловская обл. : Коммерческий центр Союза ”Чернобыль”, 1990.

5. Корнейчук В.И., Тарасенко В.П. – Вычислительные устройства на микросхемах. - 2-е изд., перераб. и доп. - Киев: Техника, 1988.

6. Нефедов А.В. – Интегральные микросхемы и их зарубежные аналоги. Справочник. Т.5. – Москва: ИП РадиоСофт, 1999.

7. Мальцев П.П. – Цифровые интегральные микросхемы: Справочник. – М. Радио и связь, 1994.

8. Будинский Я. – Логические цепи в цифровой технике. – М.: Связь, 1977.

9. Бирюков С.А. – Цифровые устройства на МОП-интегральных микросхемах. – М. Радио и связь, 1990.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.