Тема: Арифметичні пристрої

Мета роботи: дослідження типових арифметичних пристроїв – суматорів, арифметико-логічних пристроїв, помножувачів, подільників і компараторів; побудова ЦКП на суматорах і компараторах; засвоєння основ створення ієрархічного проекту на рівні блок-схеми.

Хід роботи

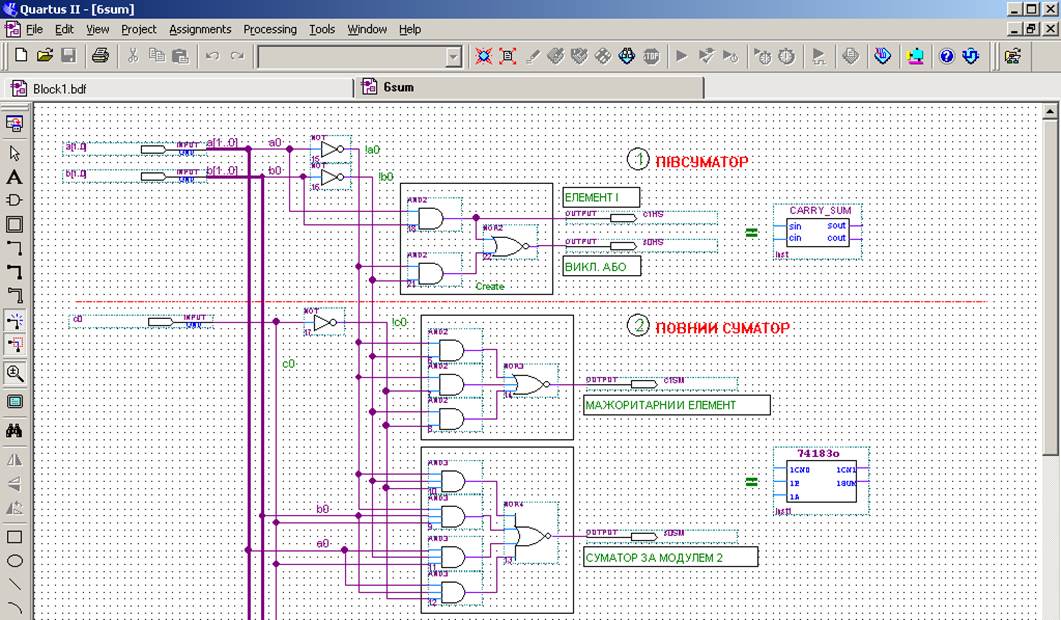

1.Запускаємо програму САПР Quartus за допомогою ярлика на робочому столі. Користуючись меню File, командою Open відкриваємо файл 6sum.bdf. У даному файлі представлена схема електрична принципова півсуматора (схема 1) і і однорозрядного повного суматора (схема 2)

Рис 1.Схема електрична принципова пів-суматора (схема 1) і однорозрядного повного суматора(схема 2)

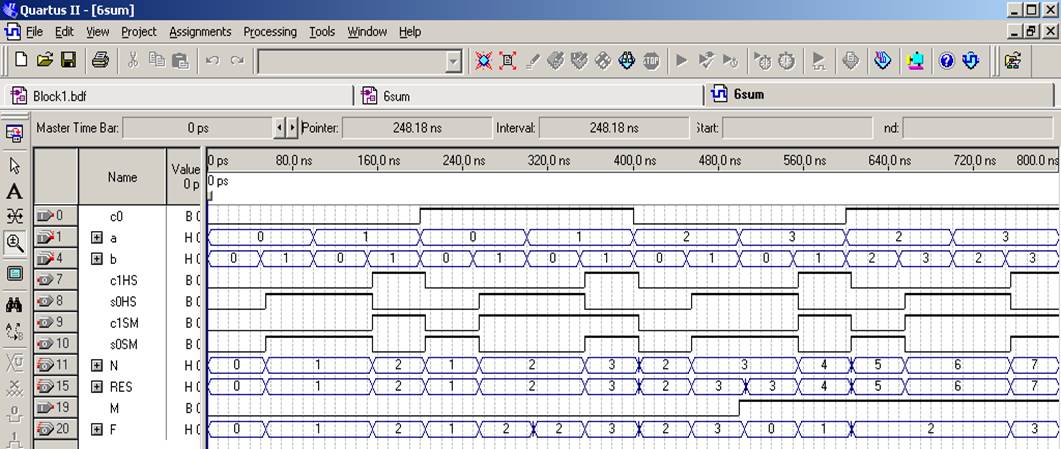

Рис 2. Осцилограмами сигналів півсуматора

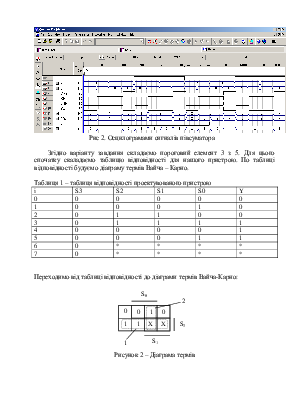

Згідно варіанту завдання складаємо пороговий елемент 3 з 5. Для цього спочатку скаладаємо таблицю відповідності для нашого пристрою. По таблиці відповідності будуємо діаграму термів Вайча – Карно.

Таблиця 1 – таблиця відповідності проектувованого пристрою

|

i |

S3 |

S2 |

S1 |

S0 |

Y |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

|

2 |

0 |

1 |

1 |

0 |

0 |

|

3 |

0 |

1 |

1 |

1 |

1 |

|

4 |

0 |

0 |

0 |

0 |

1 |

|

5 |

0 |

0 |

0 |

1 |

1 |

|

6 |

0 |

* |

* |

* |

* |

|

7 |

0 |

* |

* |

* |

* |

Переходимо від таблиці відповідності до діаграми термів Вайча-Карно:

Рисунок 2 – Діаграма термів

Згідно даної таблиці визначаємо вихідну функцію: y = S2 + S0S1.

Маючи відповідну функцію будуємо схему порогового елементу 3 з 5 користуючись САПР-ом.

Рисунок 3 – Пороговий елемент 3 з 5 у САПР

Для закріплення навичок роботи з суматорами будуємо схему, яка дозволяє виконувати додавання двійкових чисел.

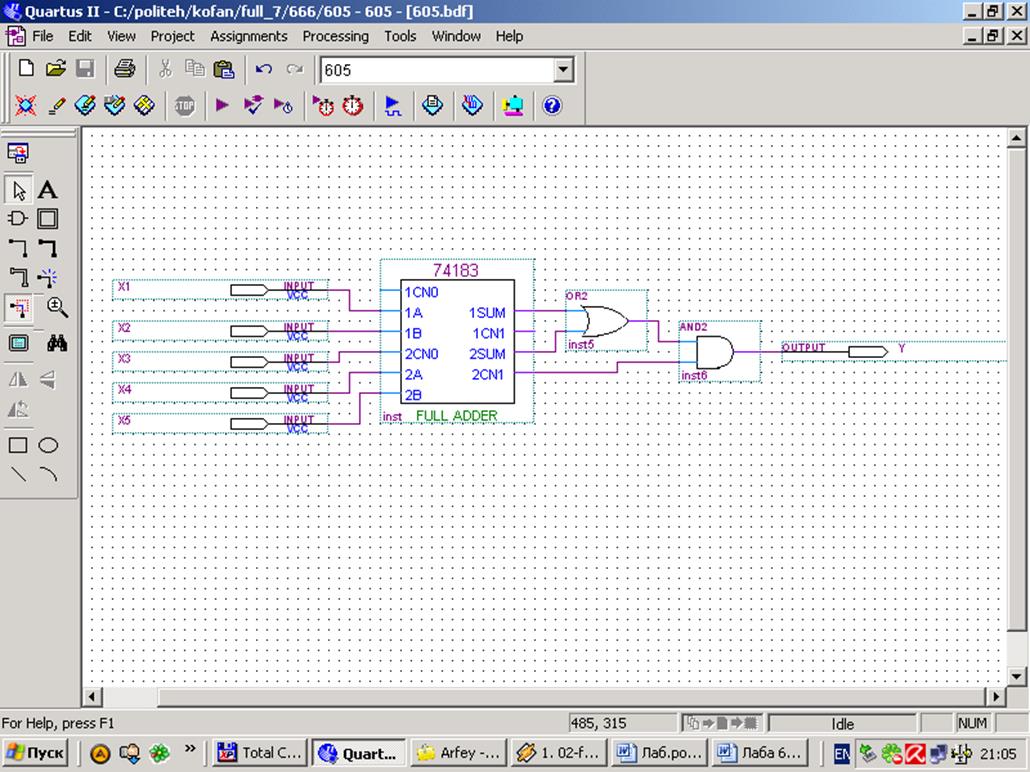

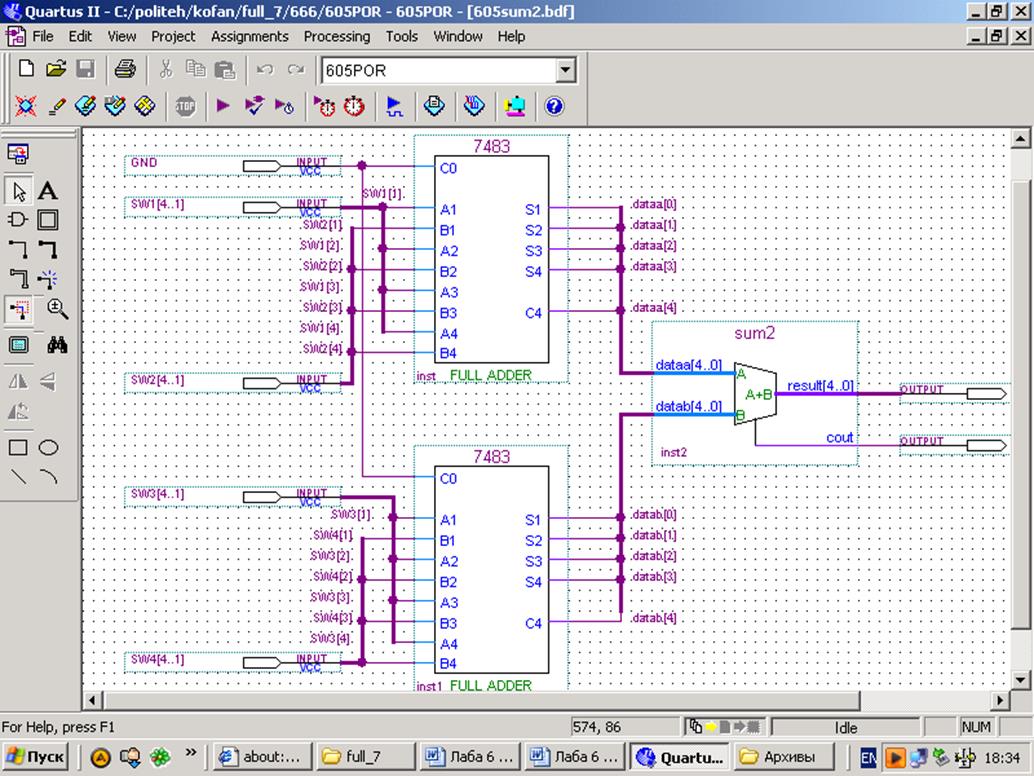

Спочатку створюємо новий проект, який називаємо 605. Додаємо до проекту проектний файл, створивши новий файл у цьому проекті. Користуючись стандартним набором макрофункції, тобто користуючись моделями мікросхем жорсткої структури у САПР будуємо схему двоступеневого суматора. Причому друга ступінь пристрою виконується з використанням мегафункції, тобто суматор, синтезований у середовищі САПР.

Рисунок 4 – Схема двоступеневого суматора у САПР

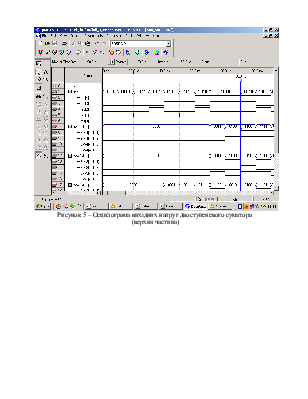

Перша ступінь цього пристрою складається з двох однакових структур, кожна з яких виконує додавання двох двійкових чисел розрядністю 4. В результаті можемо мати п’ятирозрядне двійкове число у кожній частині симетричної першої ступені. Друга ступінь виконує додавання двох п’ятирозрядних чисел. В результаті, при умові, що вхідні числа приймають великі значення можемо мати 6 – розрядне число, враховуючи розряд переносу.

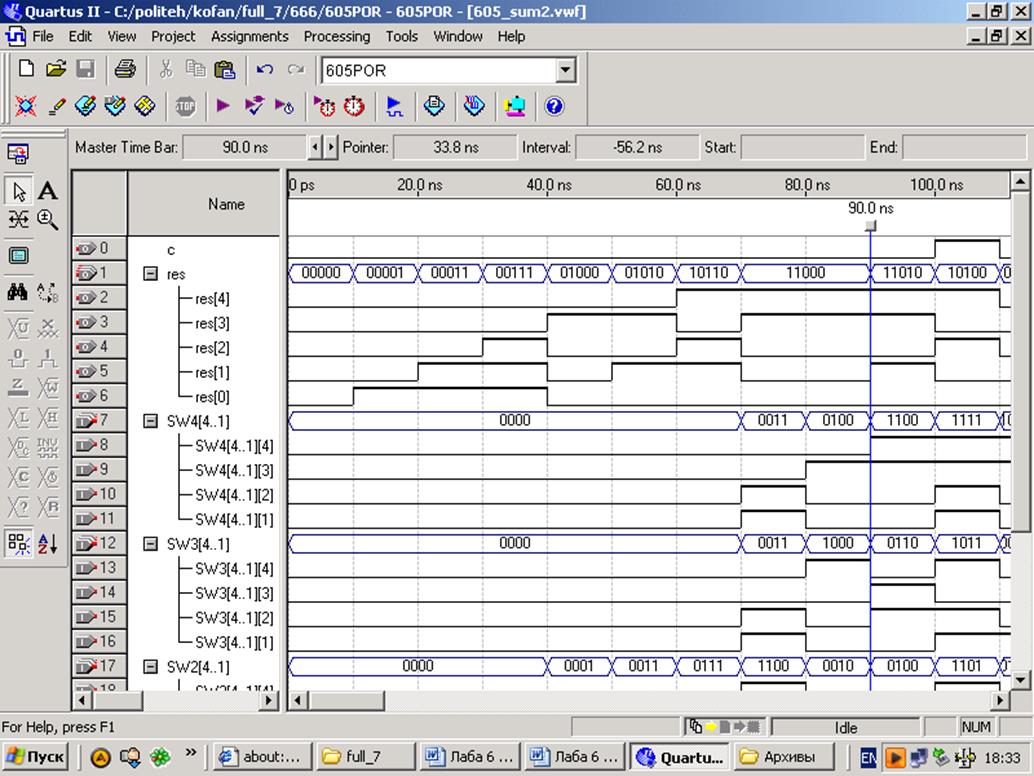

Рисунок 5 – Осцилограма вихідних напруг двоступеневого суматора

(верхня частина)

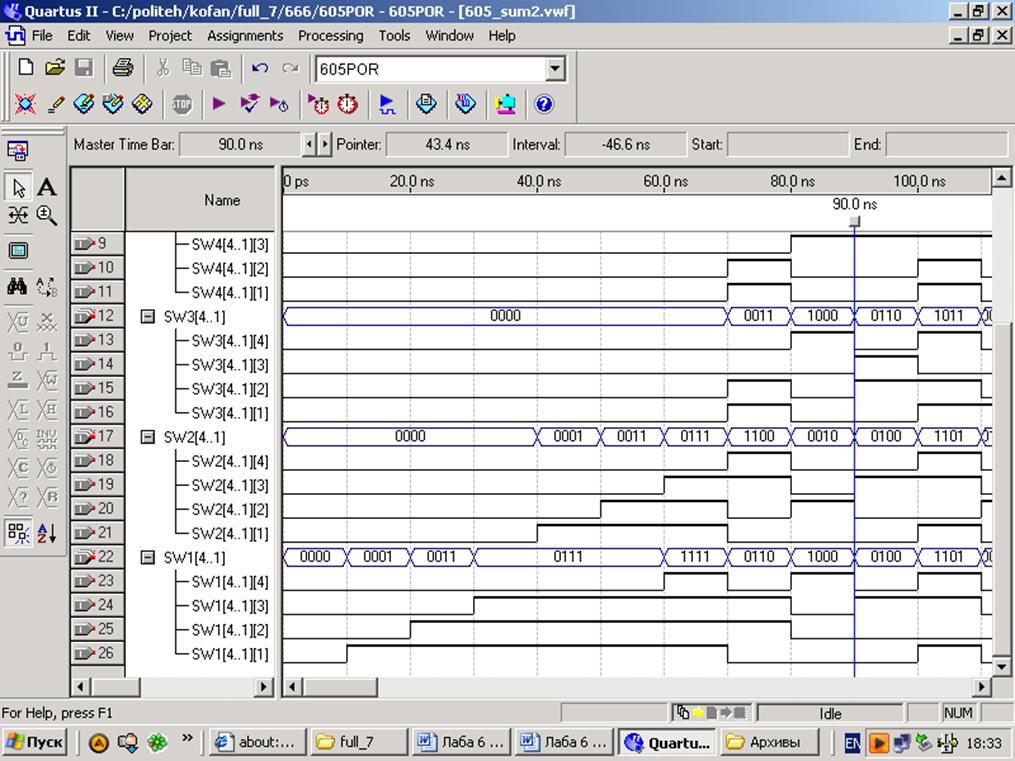

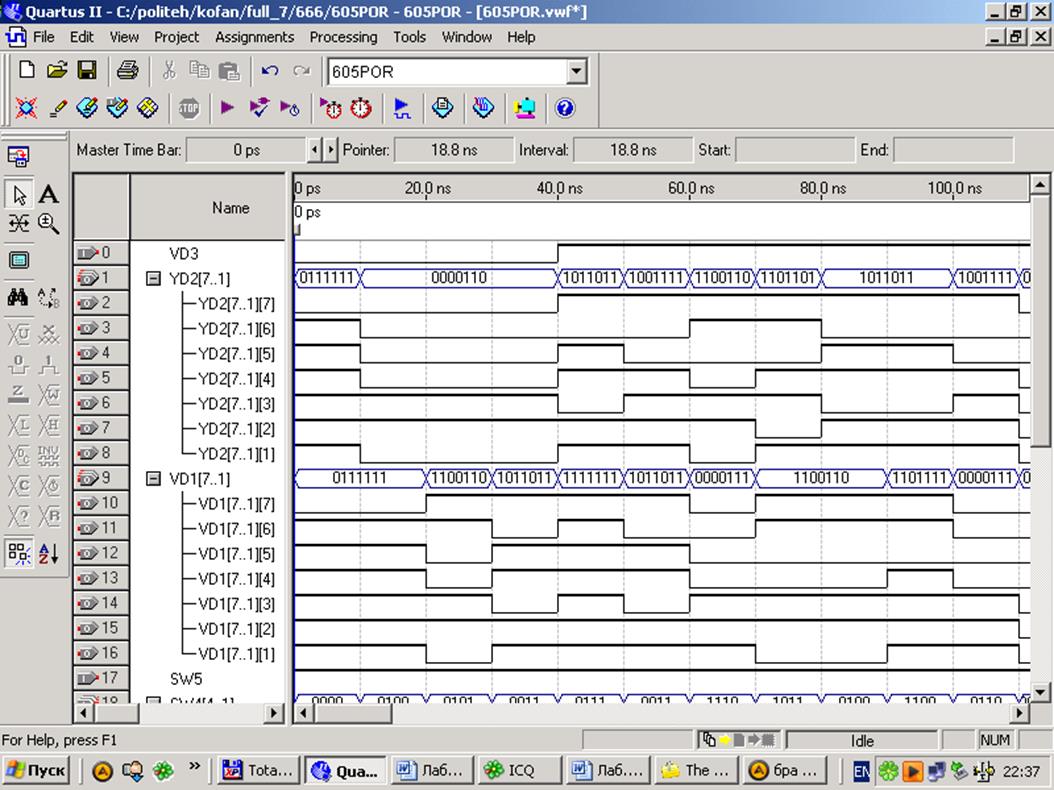

Рисунок 6 – Осцилограма вихідних напруг двоступеневого суматора

(нижня частина)

Замість вище дослідженого блоку суматора можна використовувати лише одну мікросхему, яка являє собою мікросхему програмованої структури, або, як ще називають, мікропроцесором. Для неї складаємо програму на мові високого рівня AHDL.

TITLE "блок сумування чисел" ;

INCLUDE sum2.inc ;

FUNCTION 7483 (C0, A1, B1, A2, B2, A3, B3, A4, B4);

RETURNS (S1, S2, S3, S4, C4);

SUBDESIGN 605s

(

sw1[4..1]: INPUT;

sw2[4..1]: INPUT;

sw3[4..1]: INPUT;

sw4[4..1]: INPUT;

res[5..0]: OUTPUT;

)

VARIABLE

sm1: 7483;

sm2: 7483;

sm3: sm;

BEGIN

sm1.C0=GND;

sm1.A1=sw1[1]; sm1.B1=sw2[1]; sm1.A2=sw1[2]; sm1.B2=sw2[2];

sm1.A3=sw1[3]; sm1.B3=sw2[3]; sm1.A4=sw1[4]; sm1.B4=sw2[4];

sm2.C0=GND;

sm2.A1=sw3[1]; sm2.B1=sw4[1]; sm2.A2=sw3[2]; sm2.B2=sw4[2];

sm2.A3=sw3[3]; sm2.B3=sw4[3]; sm2.A4=sw3[4]; sm2.B4=sw4[4];

sm3.dataa[]=(sm1.S1, sm1.S2, sm1.S3, sm1.S4, sm1.C4);

sm3.datab[]=(sm2.S1, sm2.S2, sm2.S3, sm2.S4, sm2.C4);

res[]=(sm3.cout, sm3.result[]);

END;

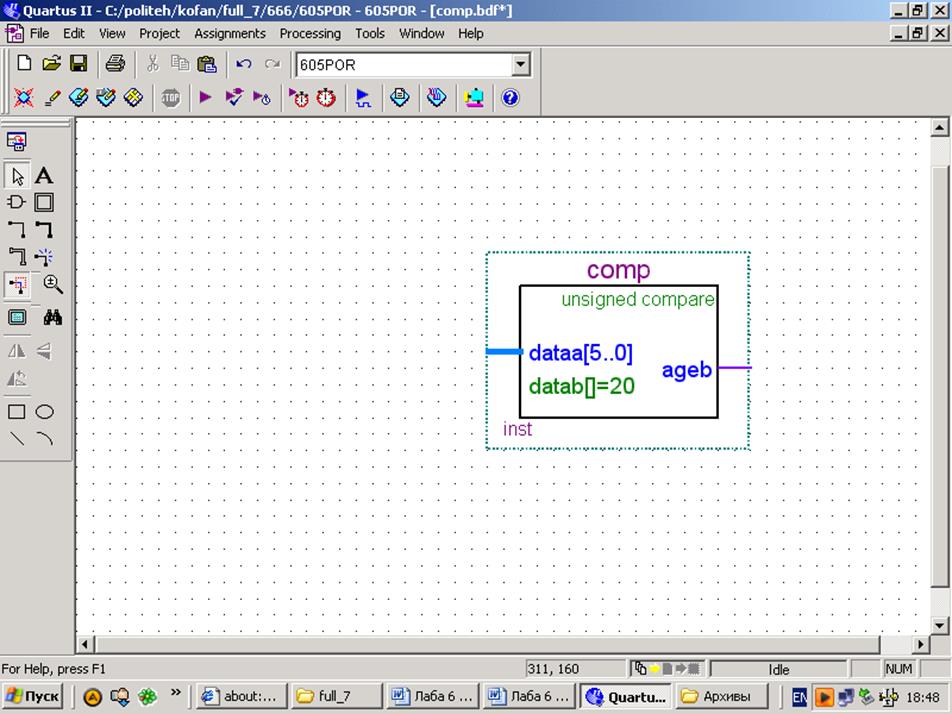

3. Засвоюємо створення ієрархічного проекту на рівні блок-схеми. Для цього спочатку створюємо окремі символи окремих блоків. Першим блоком, який нам знадобиться уже створений вище. Для використання схеми двоступеневого суматора створюємо символьний файл, який буде використовуватись у блоці. Для цього під час відкритого файлу, який ми додали до проекту вибираємо пункт меню File > Create / Update > Create Symbol file for current file. Далі для нашої блок – схеми створюємо символ схеми компаратора. У новому файлі, який також включаємо до даного проекту створюємо компаратор, користуючись мегафункцією. Створюємо компаратор, у якого на виході з’являється рівень логічного нуля, коли число, яке ми отримали в результаті розрахунків за допомогою блоку двоступеневого суматора, дамо йому назву: а, виявилось більше за константу b або дорівнювало їй. При створенні мегафункції вказуємо значення константи: b = 2010.

Створюємо символьний файл схеми компаратора.

Рисунок 7 – Створена у САПР мегафункція компаратора.

|

Рисунок 10 – Структурна схема пристрою іерархічного проекту

Згідно представленої структурної схеми пристрою будуємо блок схему пристрою.

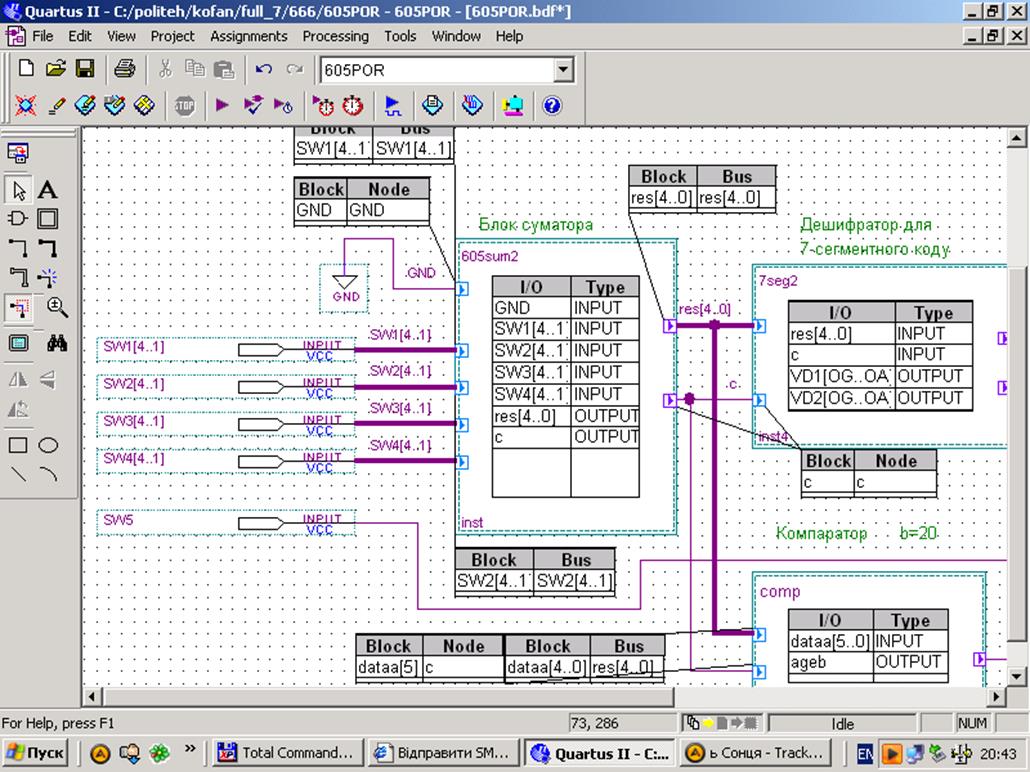

Рисунок 11 – Блок схема пристрою за іерархічним проектом (ліва частина)

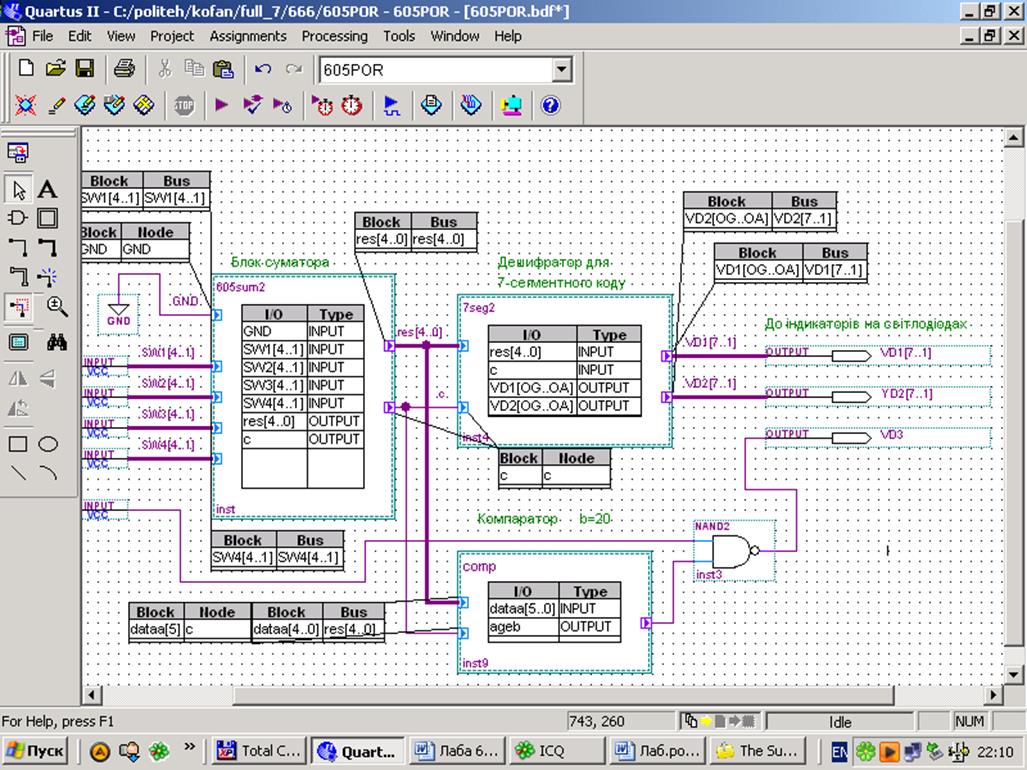

Рисунок 12 – Блок схема пристрою за іерархічним проектом (права частина)

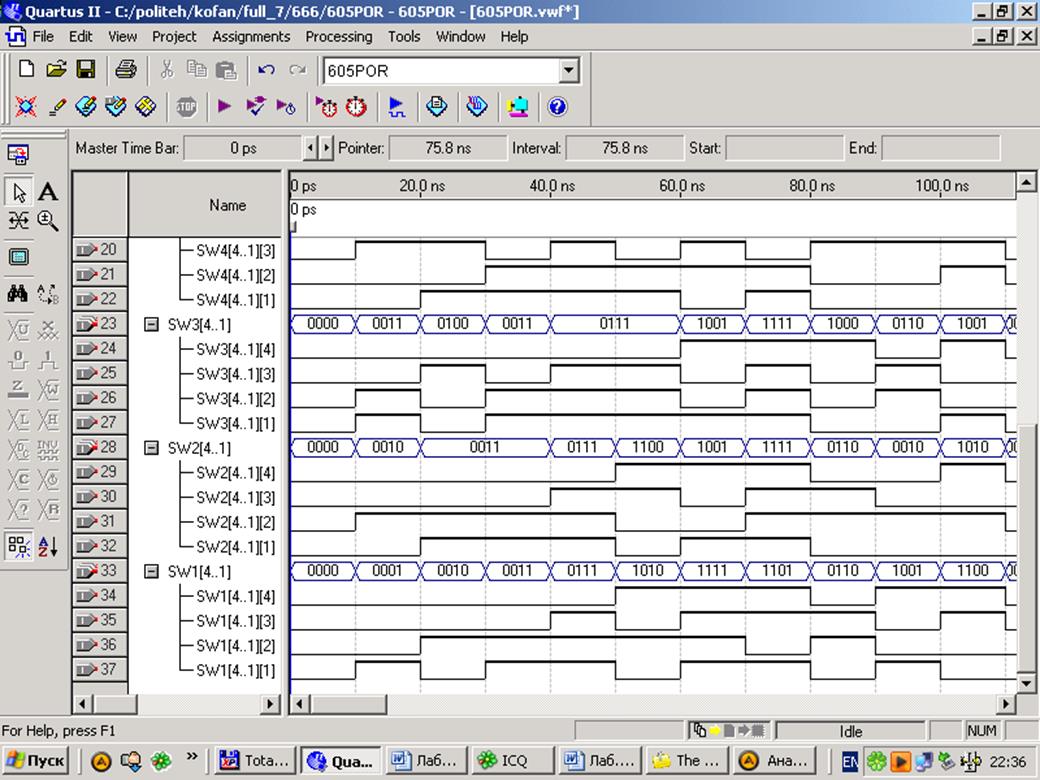

Рисунок 13 – Осцилограма пристрою, побудованого за заданою

структурною схемою (нижня частина)

Рисунок 14 – Осцилограма пристрою, побудованого за заданою

структурною схемою (верхня частина)

Висновок: В даній лабораторній роботі ми дослідили роботу суматорів та порогових пристроїв. Суматор виконує функцію арифметичного додавання чисел, причому двійкових чисел. Суматори широко використовуються у цифровій техніці. Компаратор являє собою пристрій, який порівнює два двійкових числа і при виконанні деякої умови на виході компаратора з’являється активний рівень. Тобто якщо компаратор має не інвертовані входи то буде рівень логічної одиниці. При наявності інвертованого виходу, активний рівень це є логічний 0.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.