Цифрові пристрої та мікропроцесори, ч. 2

Роздатний матеріал (рисунки до навч. посібника В. Кофанова)

1 Вступ

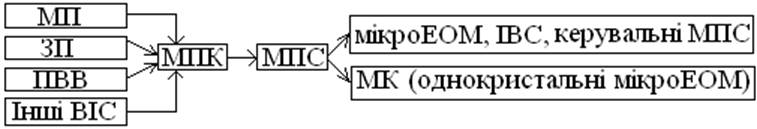

Рис. 1. Компоненти мікропроцесорної техніки

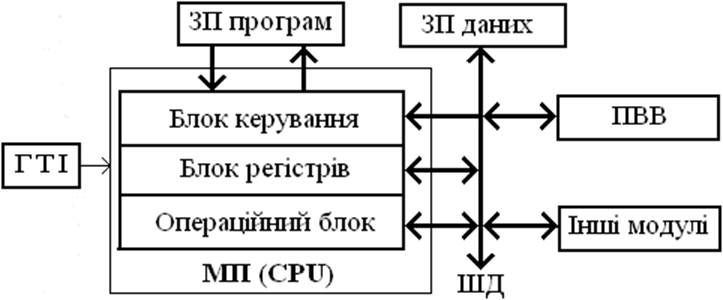

Рис. 2. Структура мікропроцесорної системи

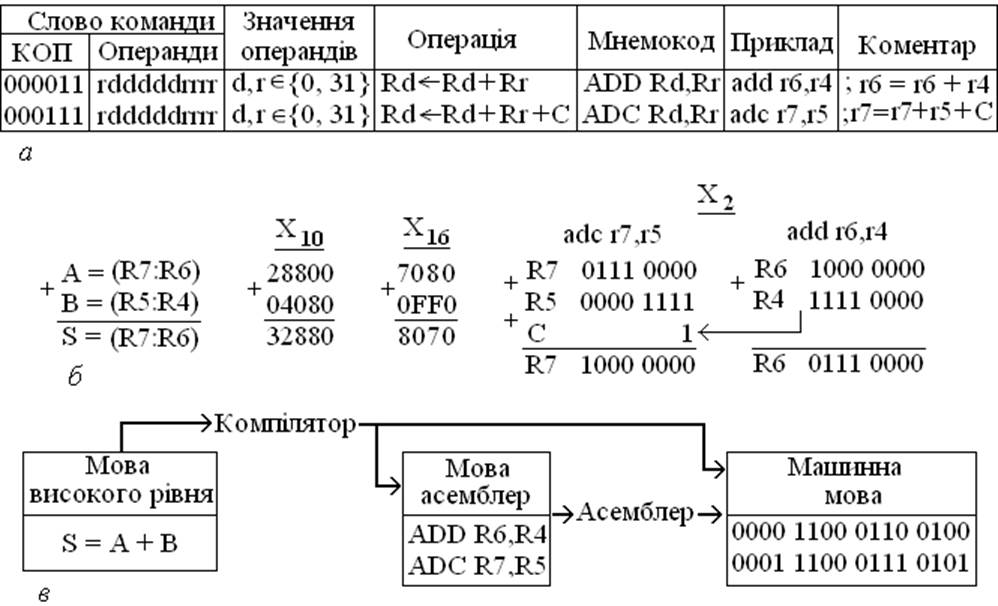

Рис. 3. Машинна мова і мова асемблера (а), приклад додавання двох 16-розрядних чисел (б) та його відображення мовами програмування (в)

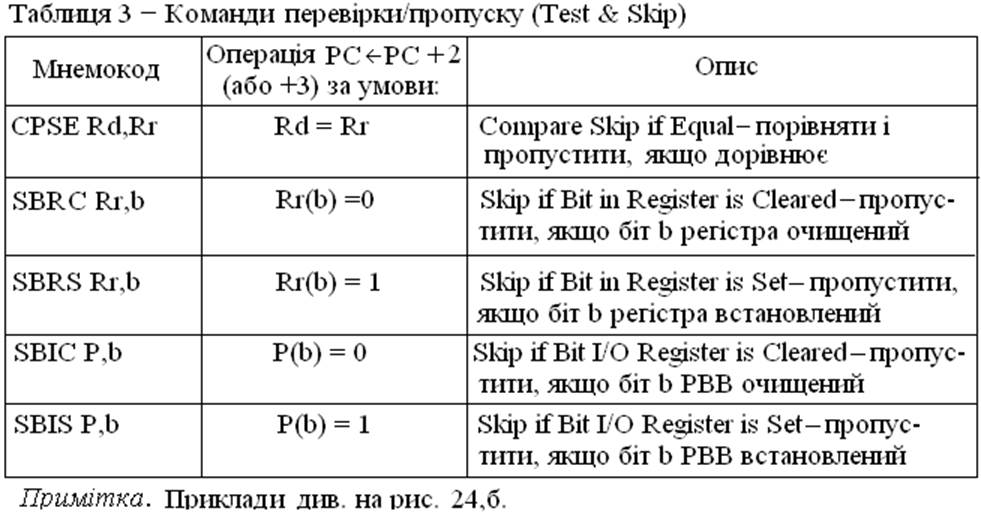

2 Архітектура МК

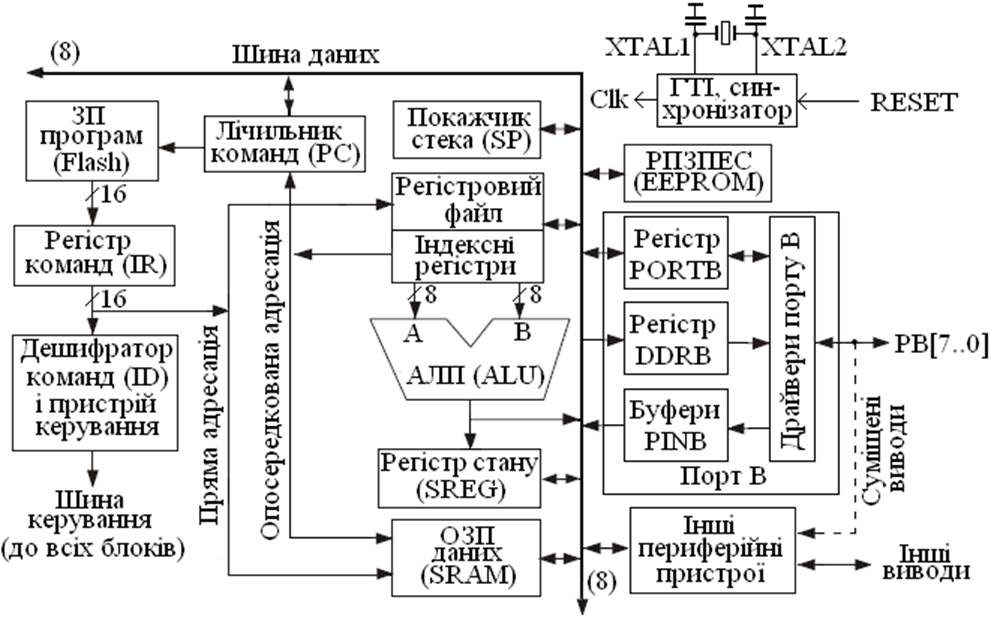

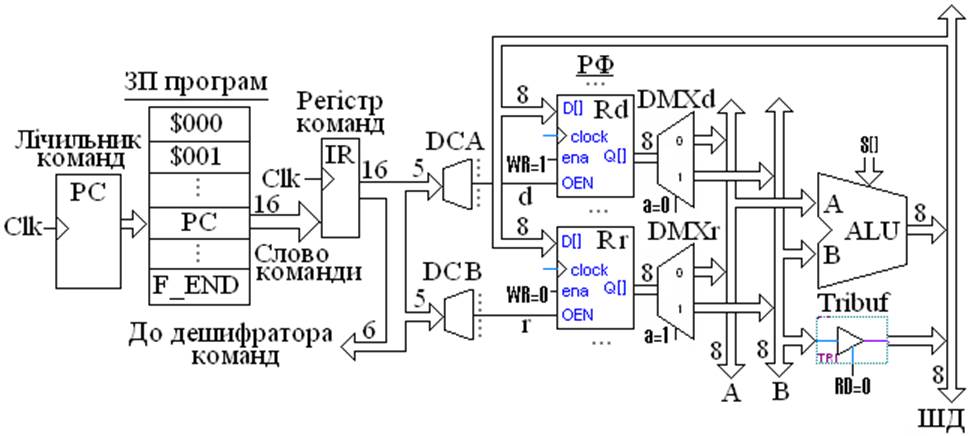

Рис. 4. Структура ядра МК AVR

Рис.5. Конвеєр команд (а) і стадії виконання операції в АЛП (б)

Рис. 6. Схема виконання команди

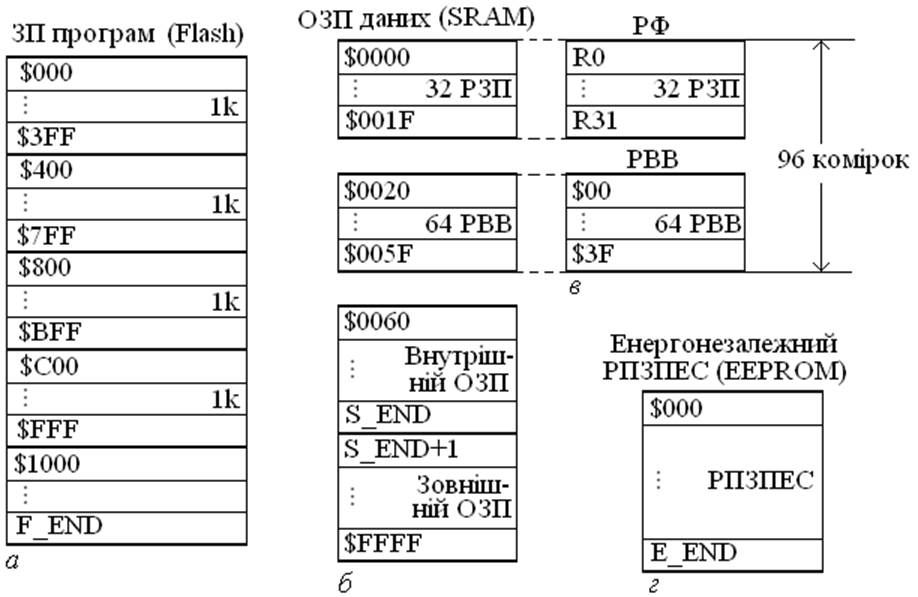

Рис. 7. Адресний простір МК: пам'яті програм (а), оперативної пам'яті

загалом (б) і регістрової пам'яті з окремою нумерацією регістрів (в)

та енергонезалежної пам'яті (г)

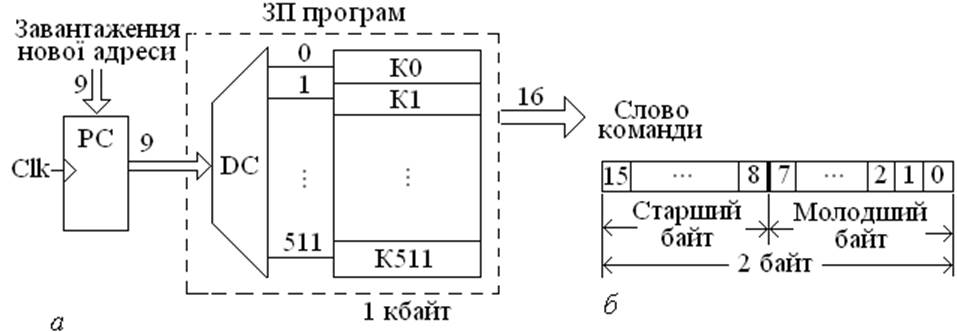

3Пам'ять програм (Flash)

Рис. 8. Загальна схема звертання до пам'яті програм (а)

і формат слова команди (б)

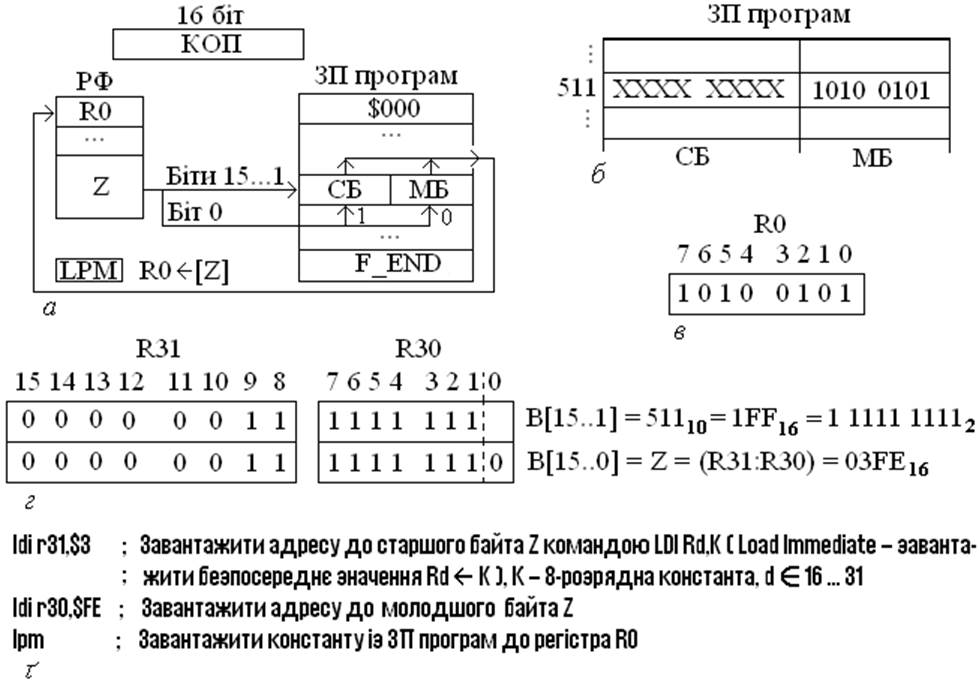

Рис. 9 Опосередкована адресація до констант пам'яті програм (а), приклад змісту молодшого байта комірки 511 ЗП програм (б), зміст регістра R0 по виконанні команди LPM (в), запис адреси до індексного регістра Z (г) та приклад програми (ґ)

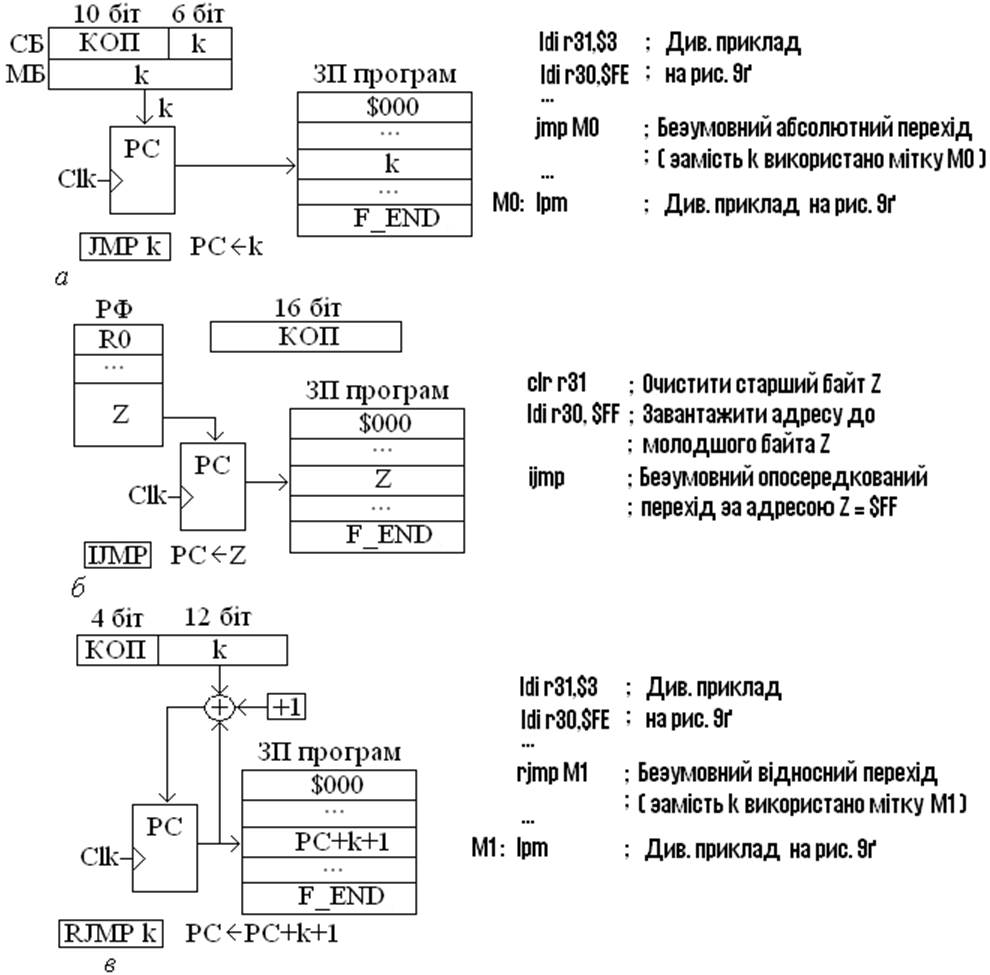

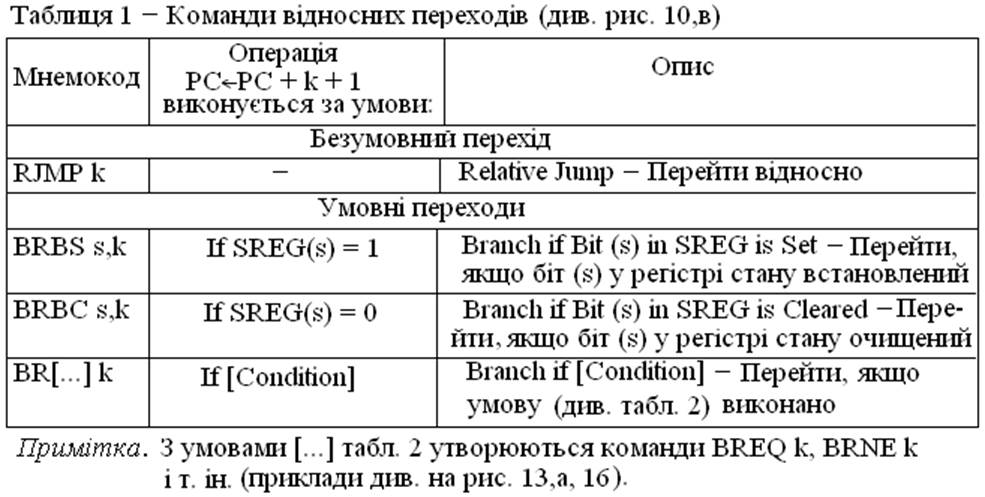

Рис. 10. Адресація переходів у програмі: абсолютна (а), опосередкована (б) та відносна (в)

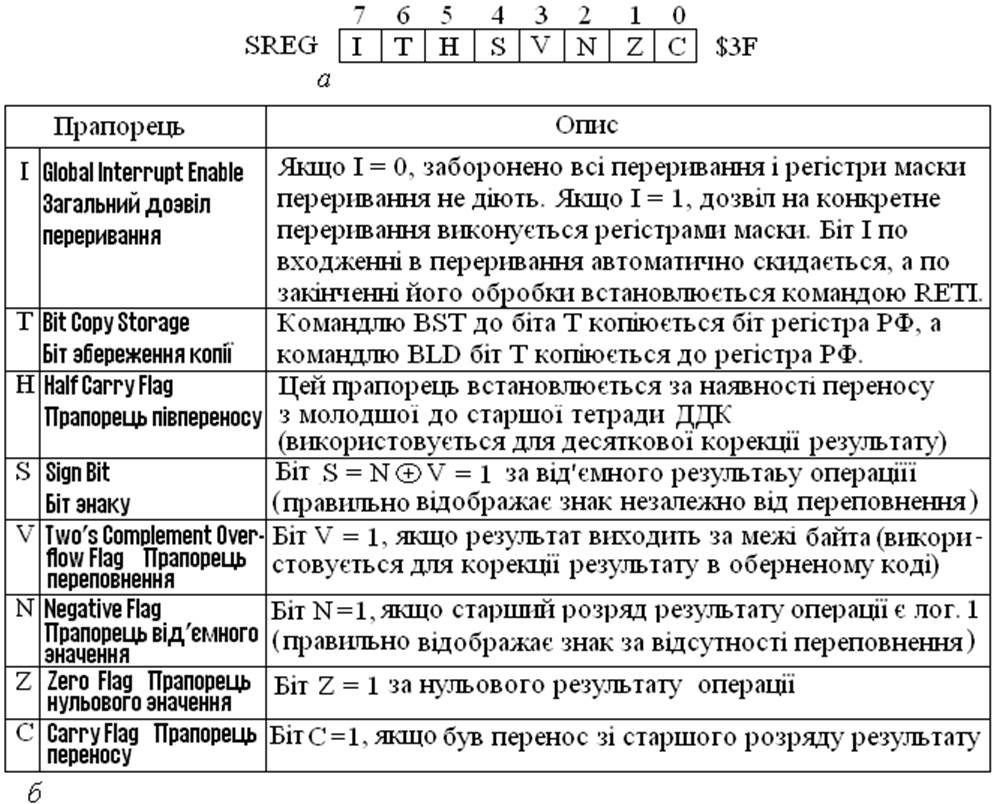

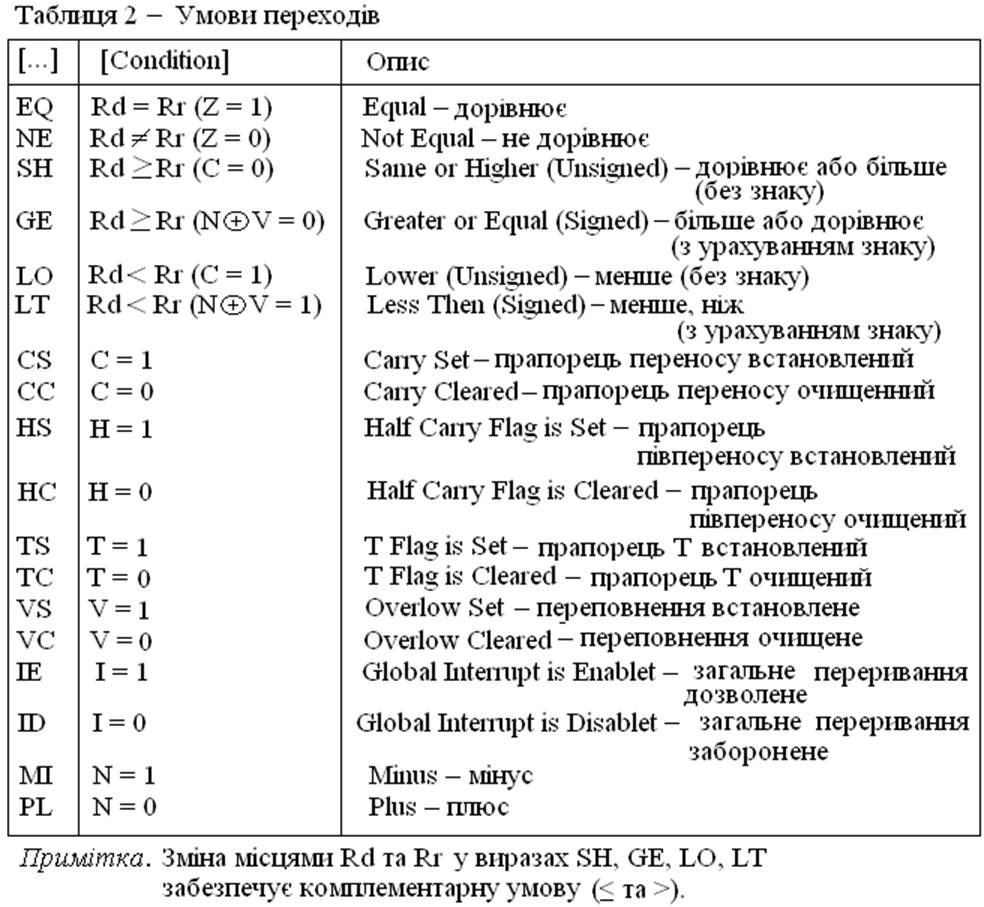

Рис. 11. Регістр стану (а) та значення його прапорців (б)

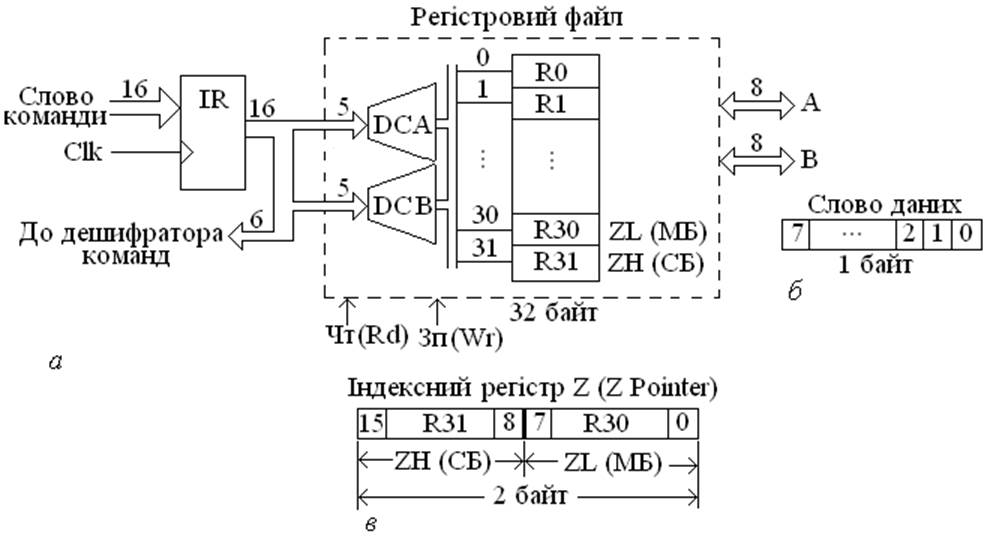

4 Регістри загального призначення

Рис. 12. Загальна схема звертання до регістрового файлу (а)

і формат слова даних (б) та індексного регістра (в)

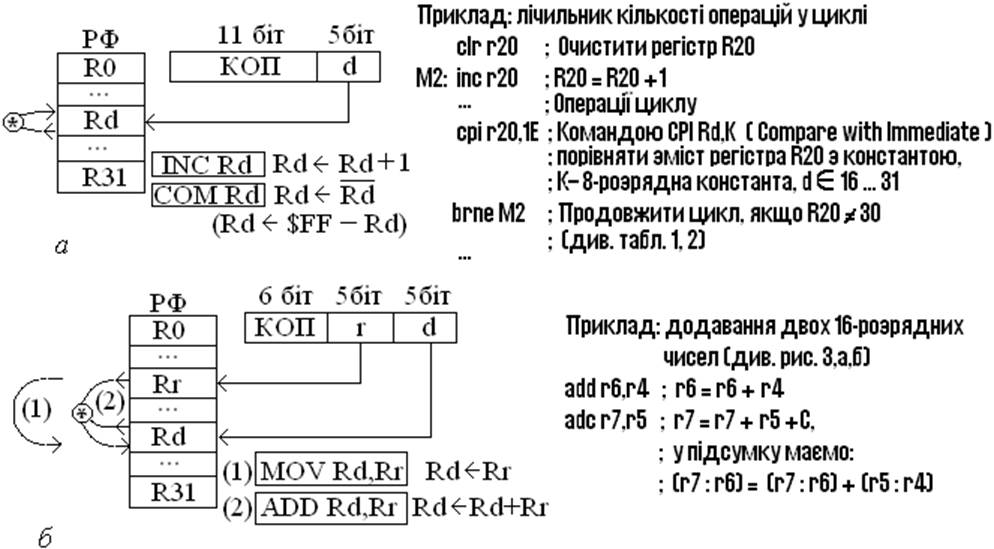

Рис. 13. Пряма

регістрова адресація до одного РЗП (а) та до двох РЗП (б)

Рис. 13. Пряма

регістрова адресація до одного РЗП (а) та до двох РЗП (б)

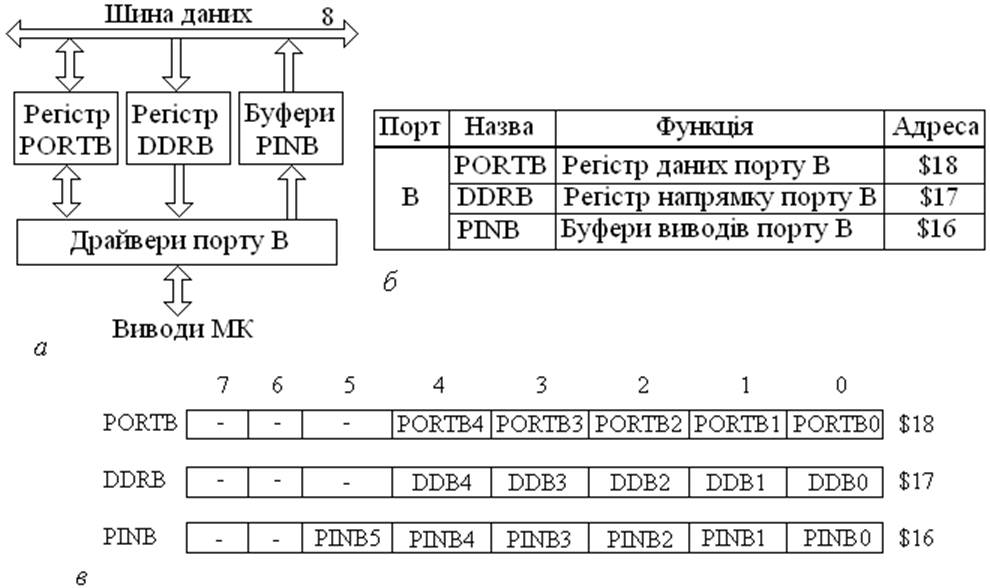

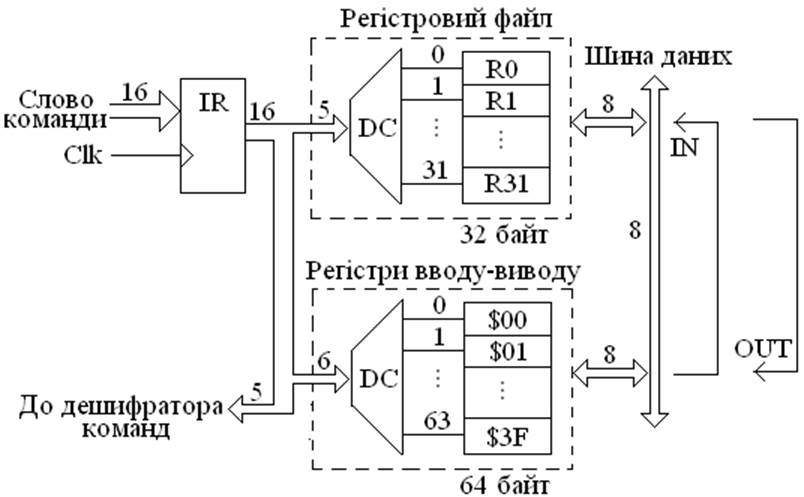

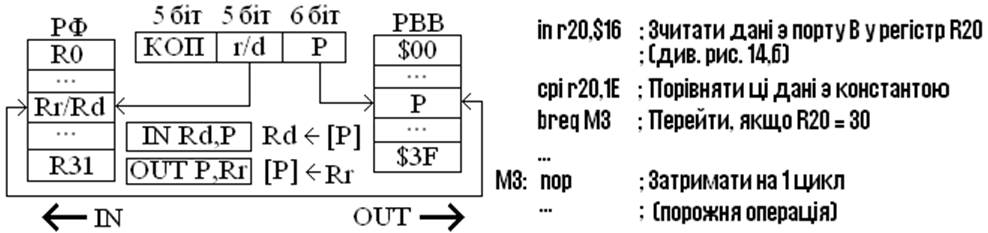

5 Паралельні порти і регістри вводу-виводу

Рис. 14. Порт вводу-виводу (а) та функції (б) і формат (в) його пристроїв в адресному просторі регістрів вводу-виводу

Рис. 15. Загальна схема звертання до регістрів вводу-виводу

Рис. 16. Пряма адресація до регістрів вводу-виводу

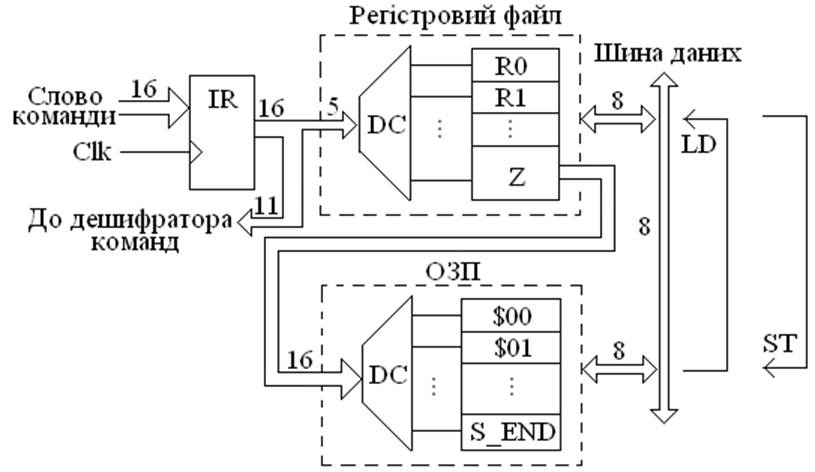

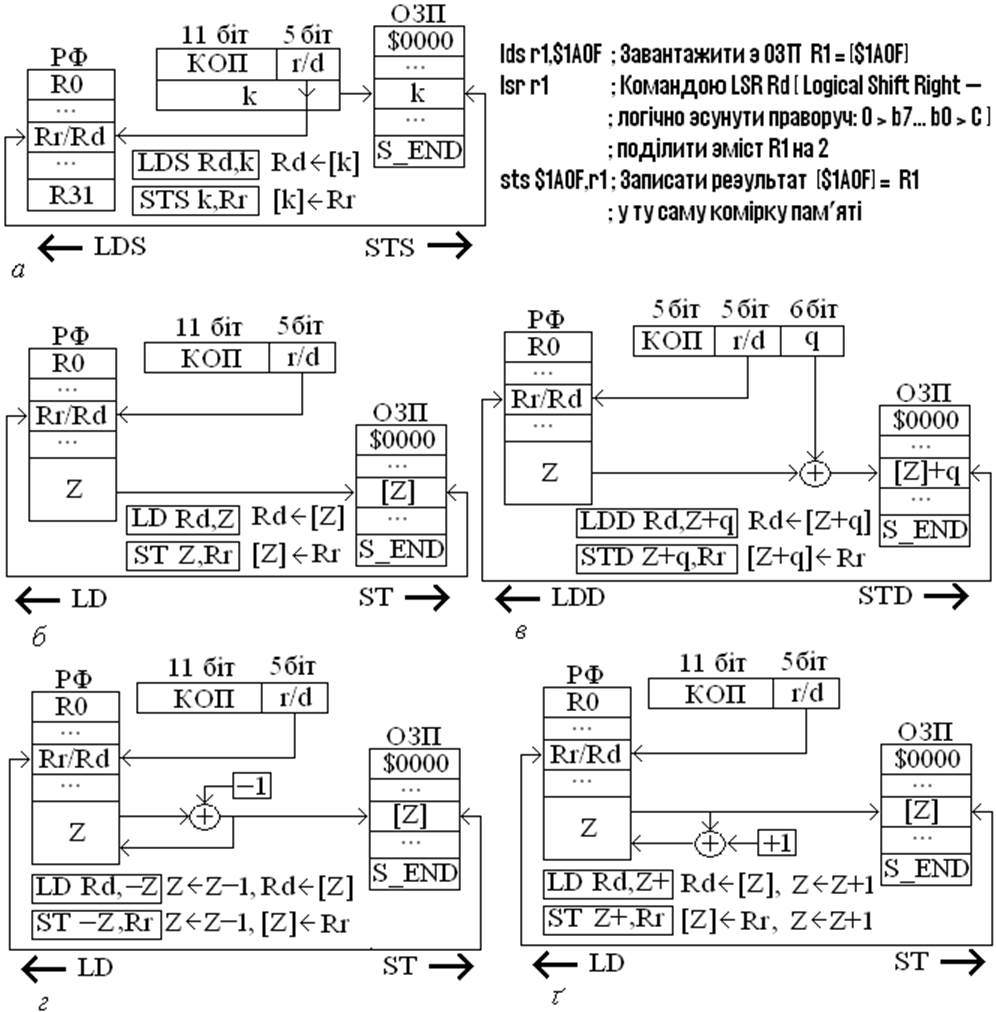

6 Внутрішня пам'ять даних (SRAM)

Рис. 17. Загальна схема звертання до ОЗП за опосередкованої адресації

Рис. 18. Адресація до ОЗП – пряма (а) та опосередкована: проста (б), зі зміщенням (в), з переддекрементом (г) та з постінкрементом (ґ)

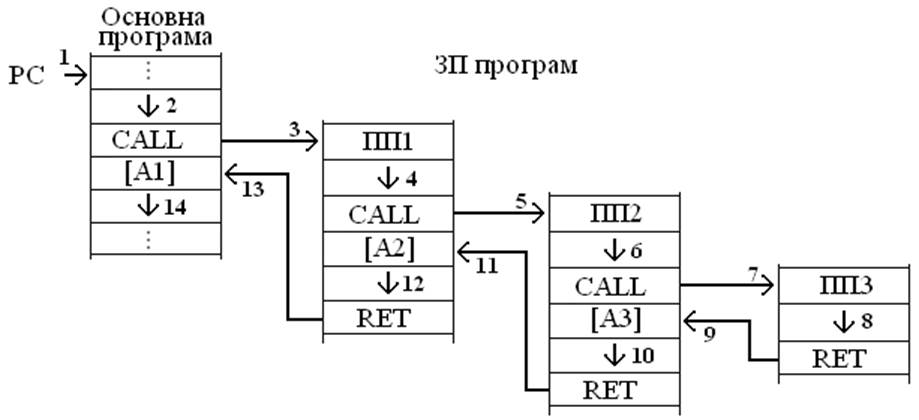

7 Стек

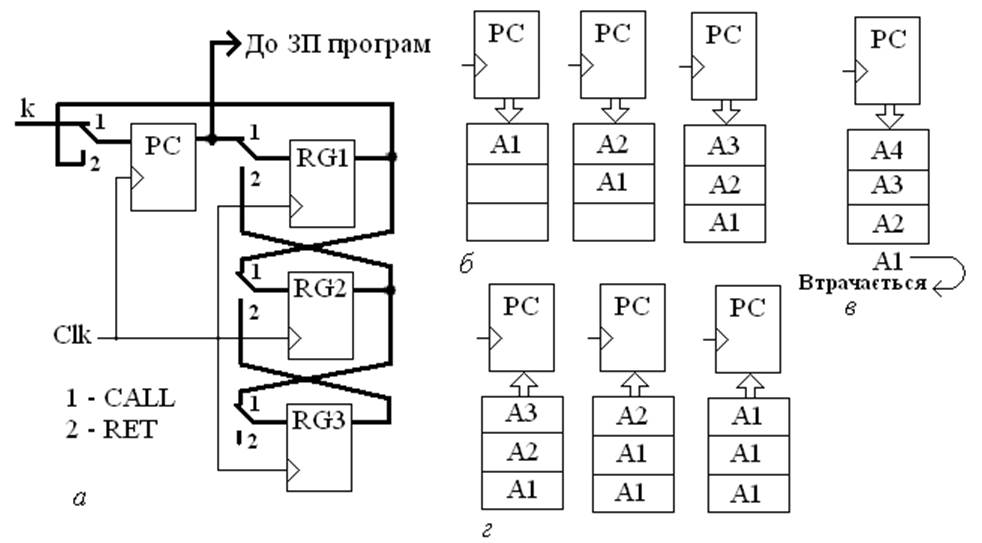

Рис. 19.Галуження програми

Рис. 20.Апаратний стек (а) і схеми введення до стека (б), введення із втратою даних (в) та виведення зі стека (г)

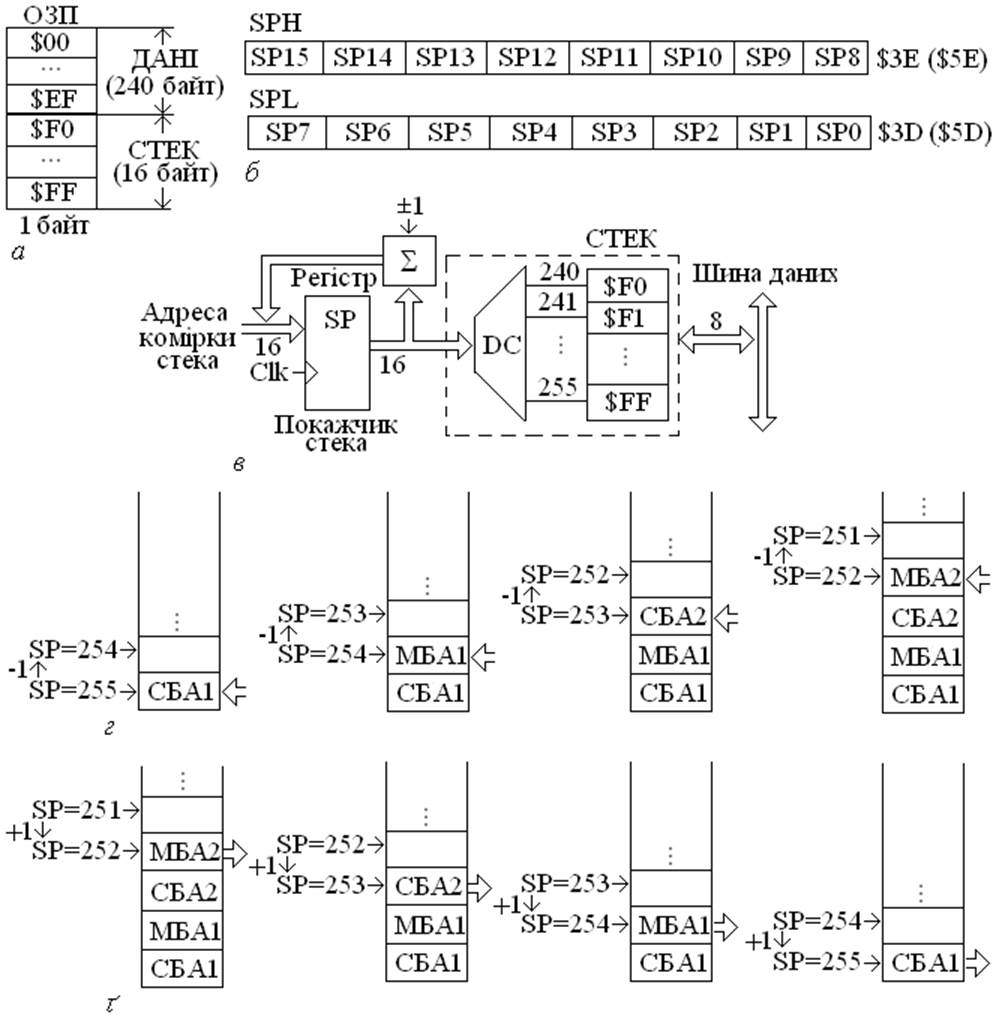

Рис. 21.Програмний стек (а), формат РВВ – покажчика стека (б), загальна схема звертання до стека (в) і схеми введення до стека (г) та виведення зі стека (ґ)

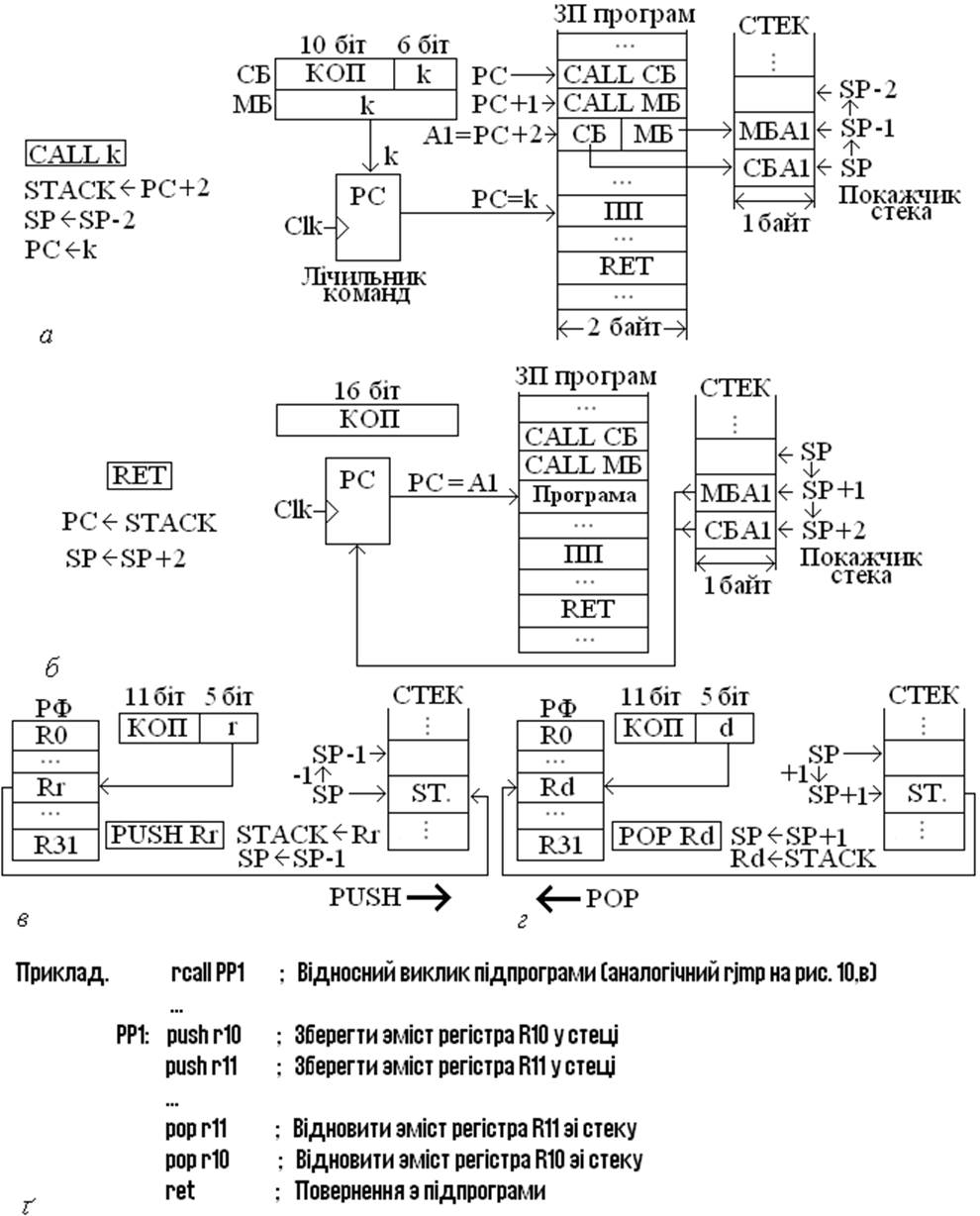

Рис. 22. Адресація, пов’язана зі стеком: виклику підпрограми (а), повернення з підпрограми (б), запису даних до стека (в), зчитування їх зі стека (г) та приклад (ґ)

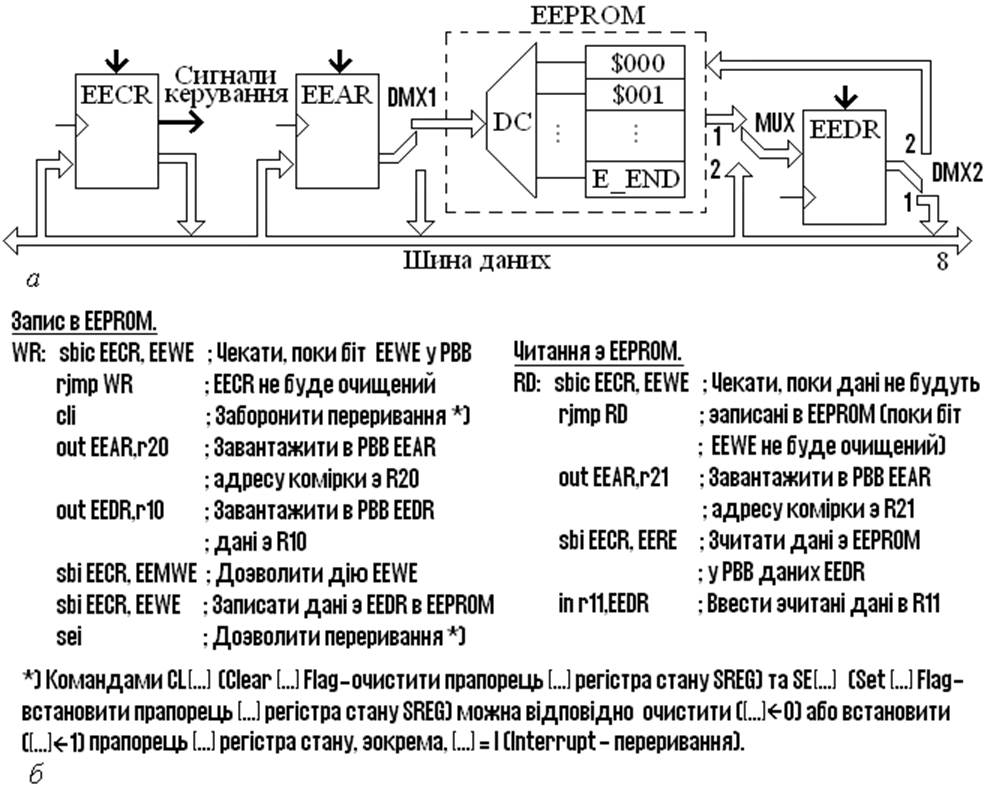

8 Енергонезалежна пам'ять (EEPROM)

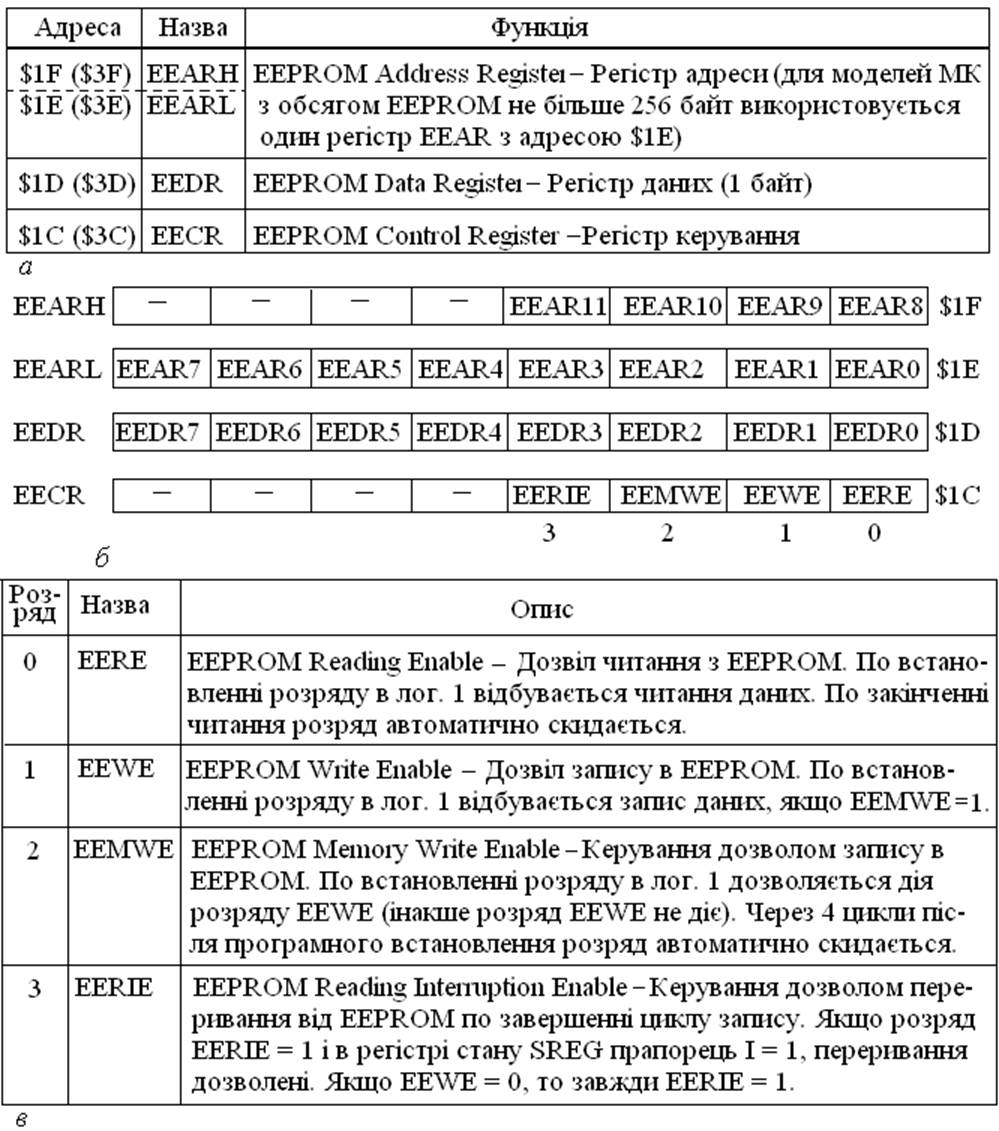

Рис. 23. Регістри доступу до енергонезалежної пам'яті (а), їх формат в адресному просторі РВВ (б) та розряди регістра EECR (в)

Рис. 24. Загальна схема звертання до енергонезалежної пам'яті (а) та приклади (б) запису і зчитування (за обсягу EEPROM до 256 байт)

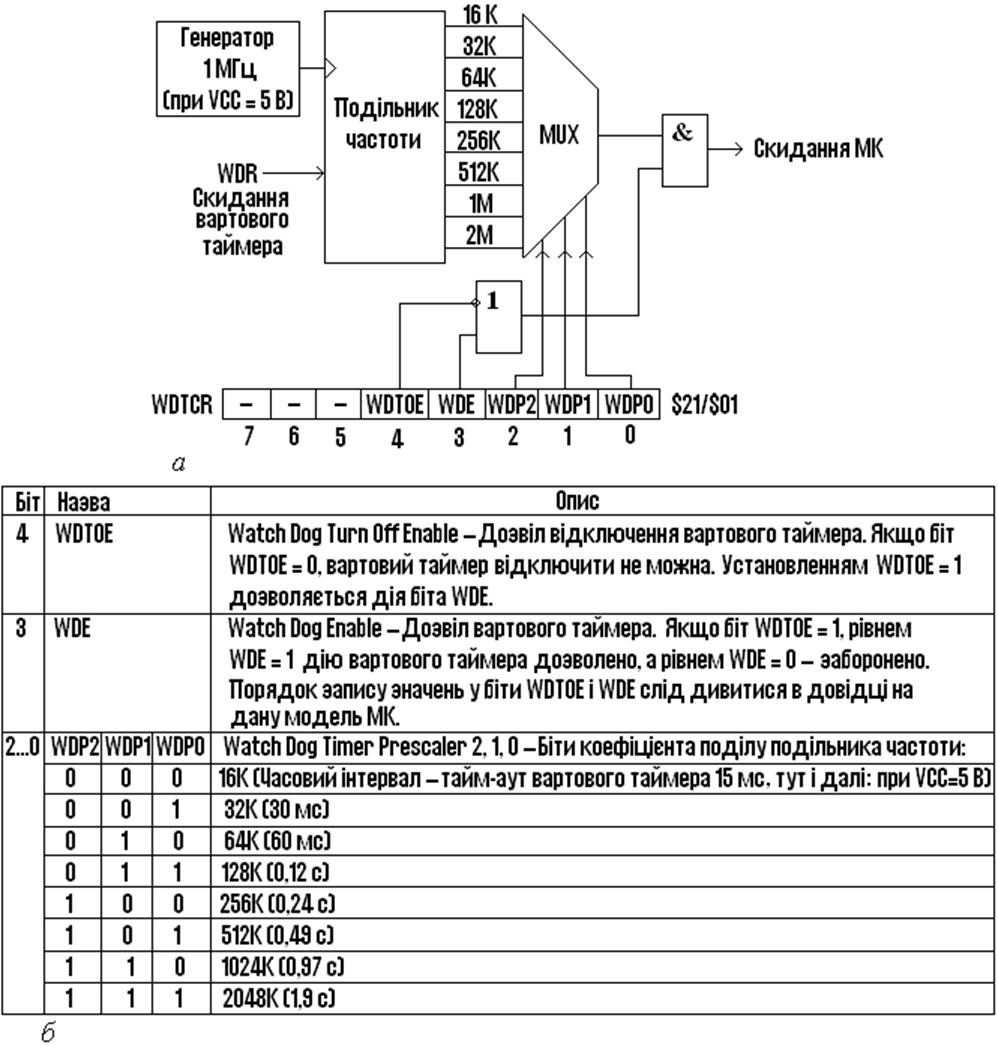

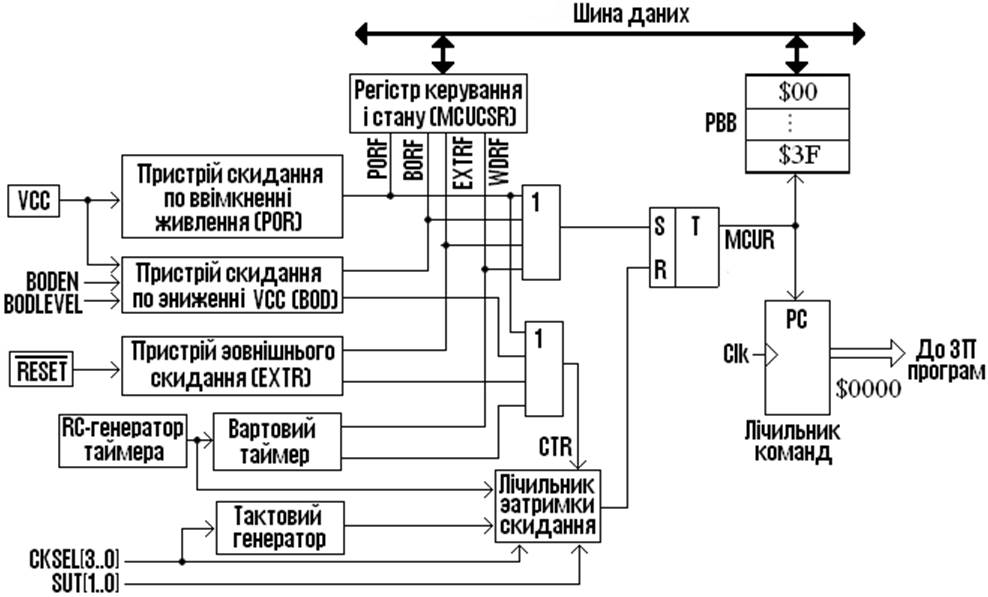

9 Система скидання МК

Рис. 25. Вартовий таймер і регістр керування вартовим таймером (а) та розряди цього регістра (б)

Рис. 26. Узагальнена схема скидання МК

Рис. 26. Узагальнена схема скидання МК

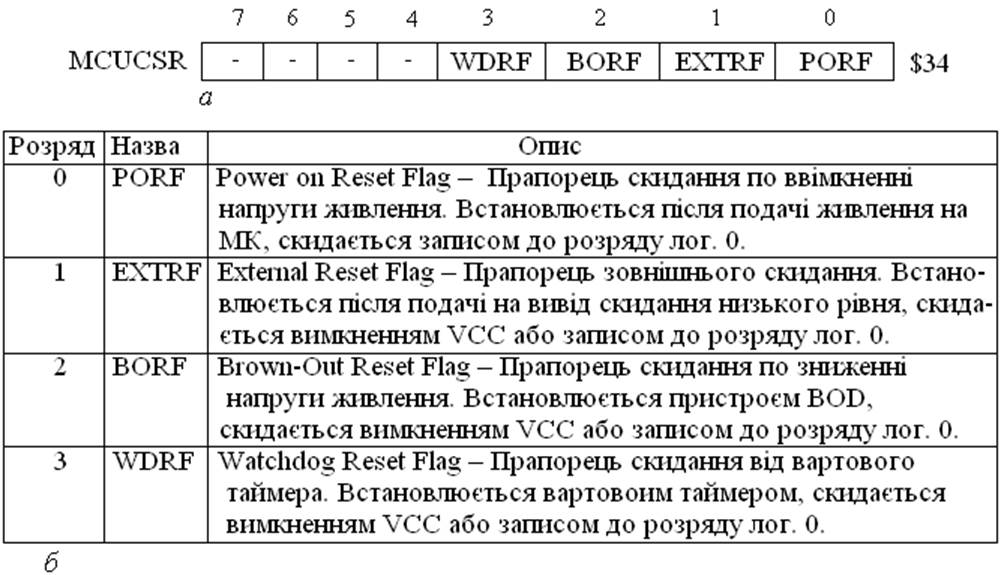

Рис. 27. Формат регістра керування скиданням і стану МК (а)

та його розряди (б)

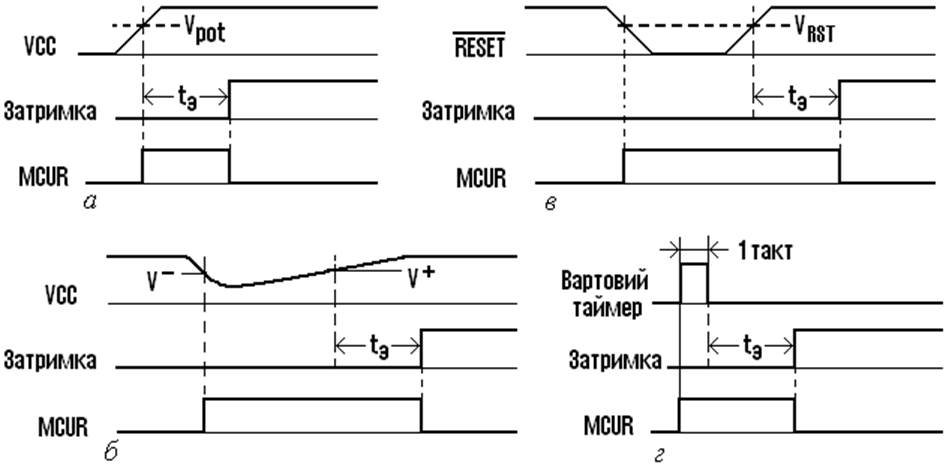

Рис. 28. Часові діаграми скидання МК по ввімкненні напруги живлення (а),

по зниженні напруги живлення (б), по виводу скидання МК (в)

та по вартовому таймеру (г)

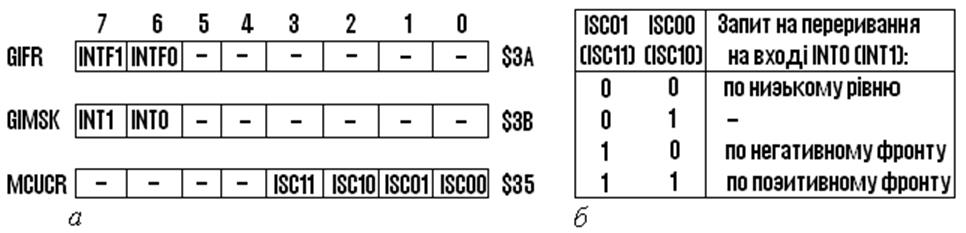

10 Система переривань МК

|

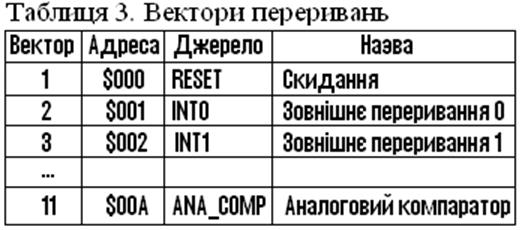

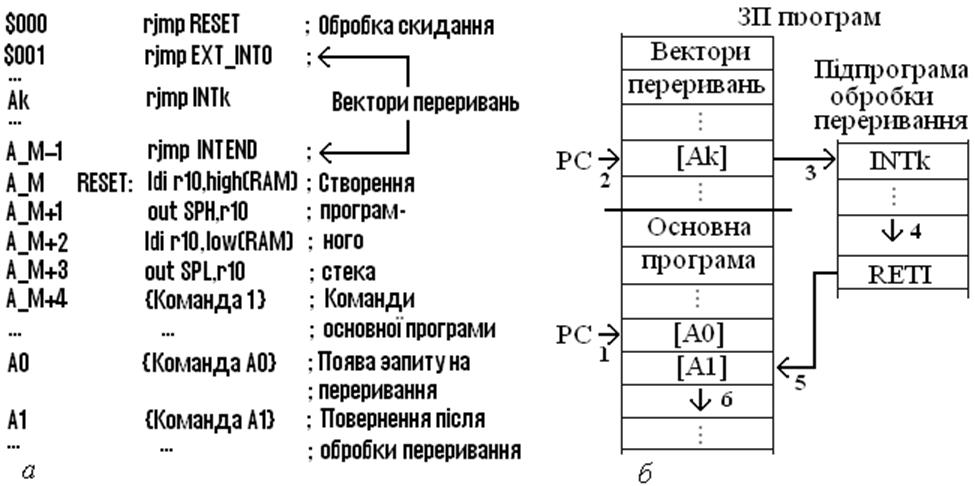

Рис. 29. Приклад розміщення векторів переривань (а) і

порядок виконання команд (б)

Рис. 30. Типові регістри, що керують перериваннями (а): GIFR – загальний регістрпрапорців переривань, GIMSK – загальний регістрмаски переривань і MCUСR – регістр керування мікроконтролером та розряди регістра MCUСR (б)

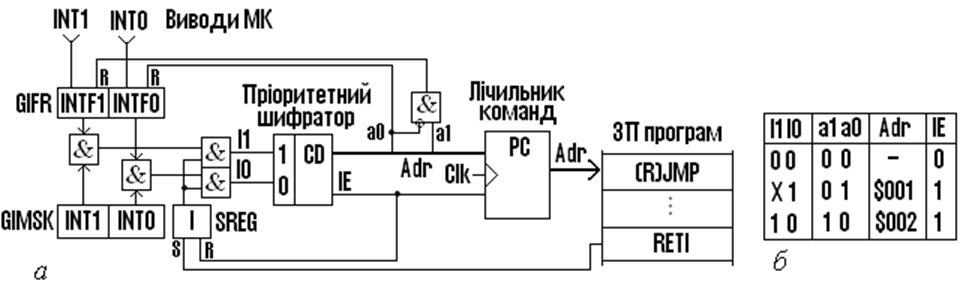

Рис. 31. Узагальнена схема зовнішніх переривань МК (а)

і таблиця відповідності пріоритетного шифратора (б)

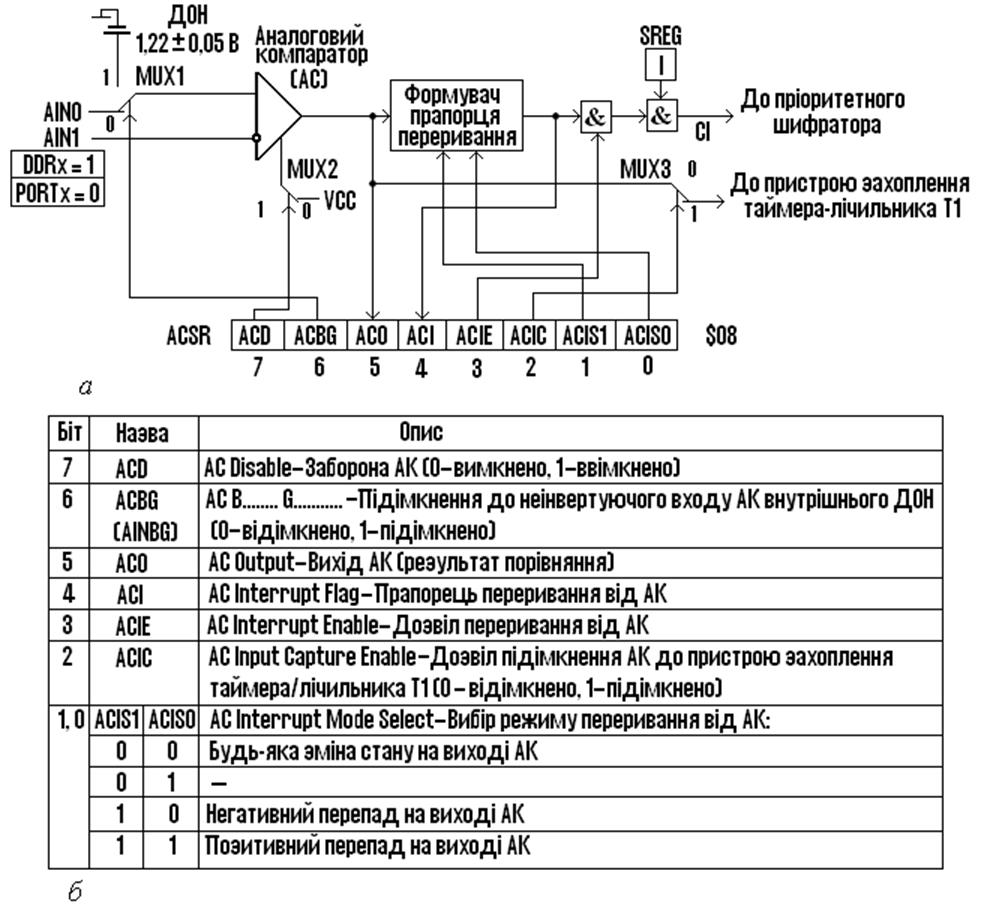

11 Аналоговий компаратор

……………………………………….

Рис. 32

Рис. 33. Структурна схема аналогового компаратора і формат регістра стану і керування АК (а) та розряди цього регістра (б)

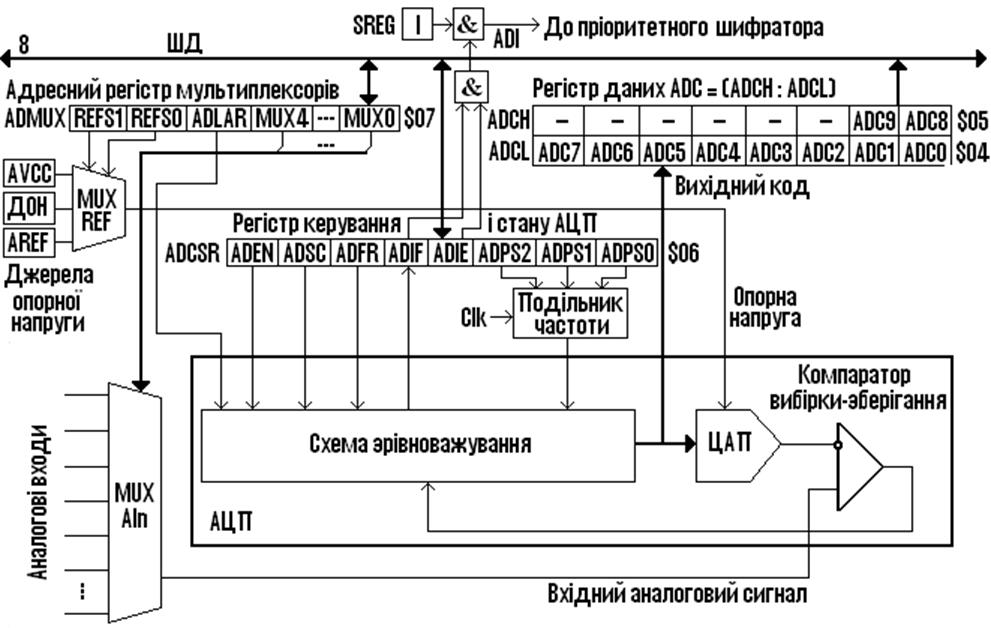

12 ЦАП і АЦП

……………………………………….

Рис. 34, 35

Рис. 36. Модуль аналогово-цифрового перетворювача

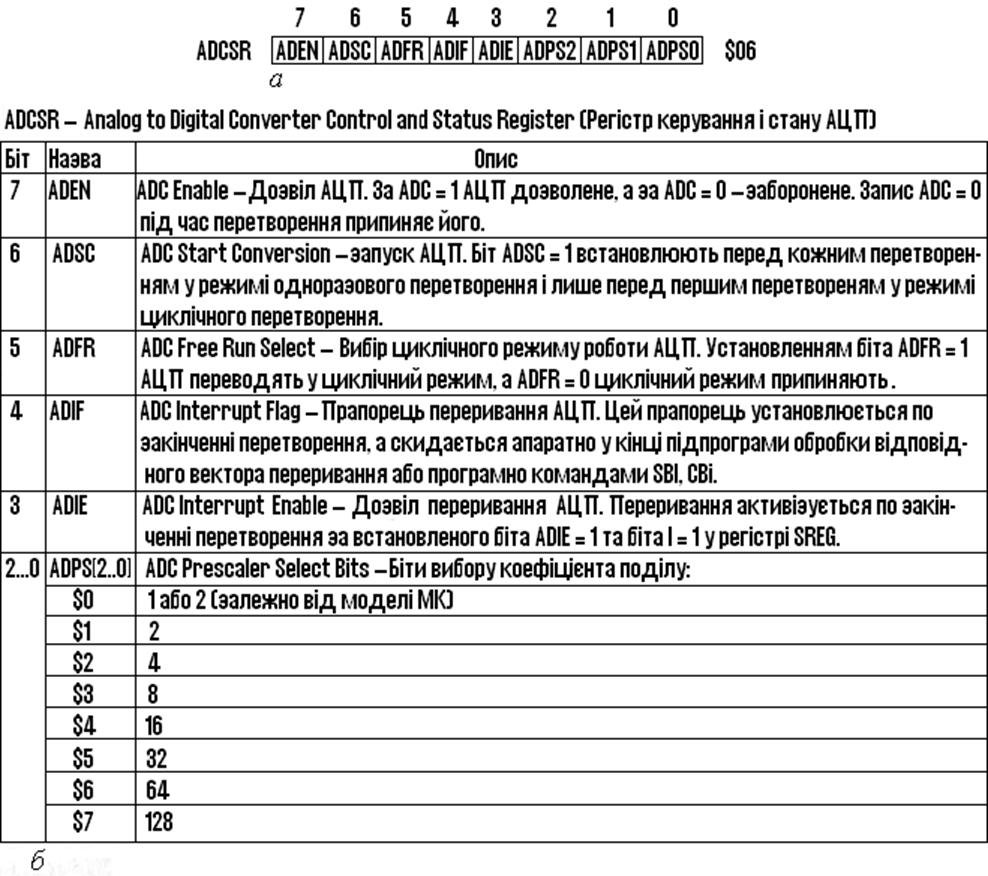

Рис. 37. Формат регістра керування і стану АЦП (а) та його біти (б)

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.