3.3 Виконати автоматичне проектування пристрою за п. 3.1, 3.2 (на ВІС програмованої структури родини FLEX10K) на доцільному рівні (тригерні примітиви, макрофукції, мегафункції за автоматичного створення їх зразка) у графічному редакторі Quartus II та здійснити автоматичний аналіз швидкодії. Навести потрібні файли проекту із зазначенням його імені з варіантом XX та дати стисле тлумачення результатів, порівняти їх з результатами проектуванням вручну за п.3.1, 3.2.

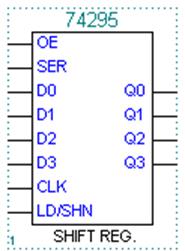

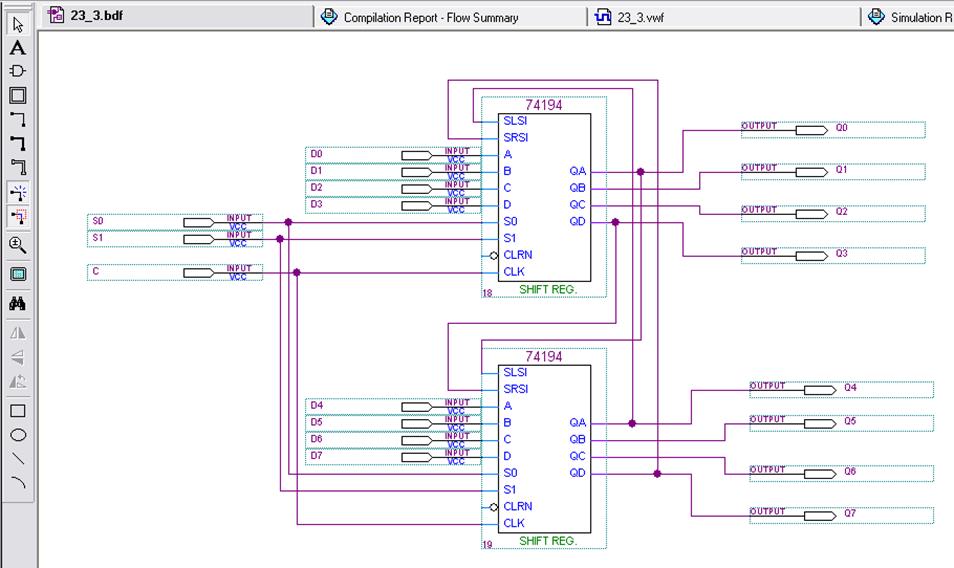

Для реалізації необхідного завдання в програмі Quartus II використаємо 4-ох розрядний регістр типу:

В розгортці ця мікросхема має наступний вигляд:

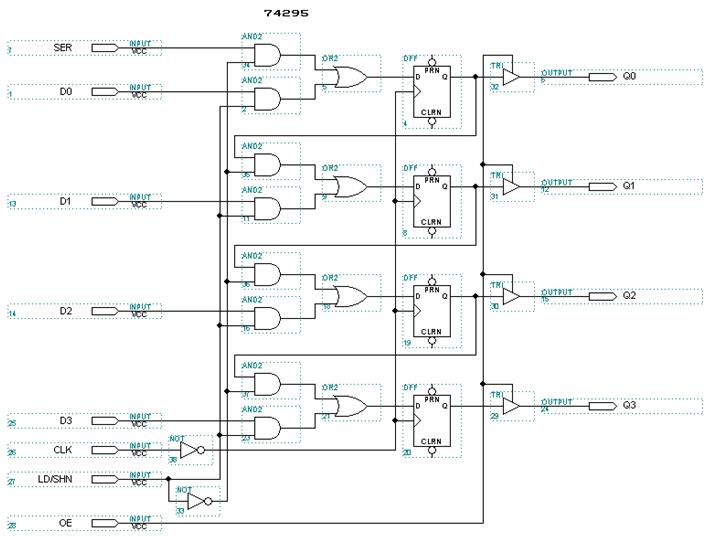

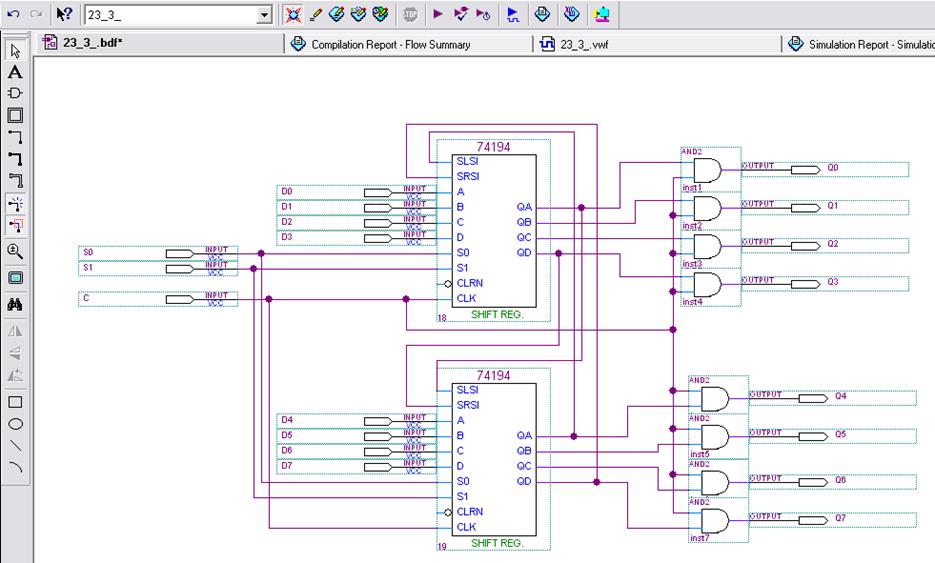

Так як ця мікросхема є 4-ох розрядною, нам необхідно буде використати дві таких мікросхеми, після з’єднання схема буде наступна:

Реалізація розподільника рівнів на 8 каналів (згідно з варіантом):

Проектування пристрою у графічному редакторі Quartus II:

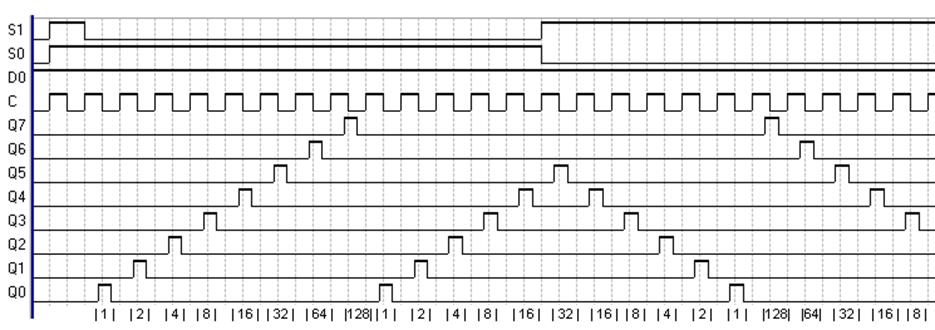

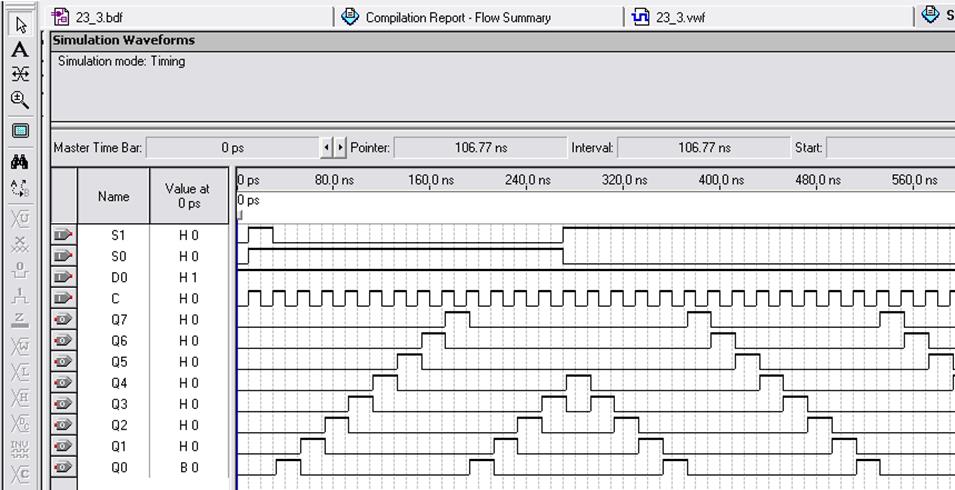

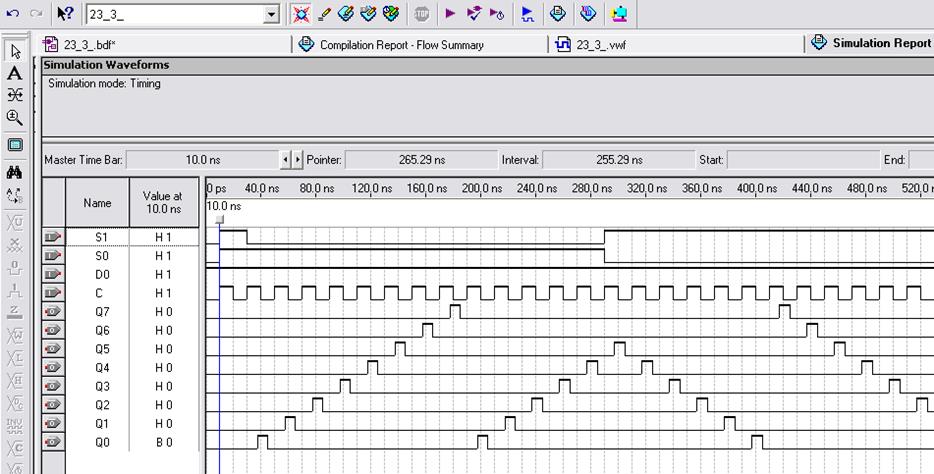

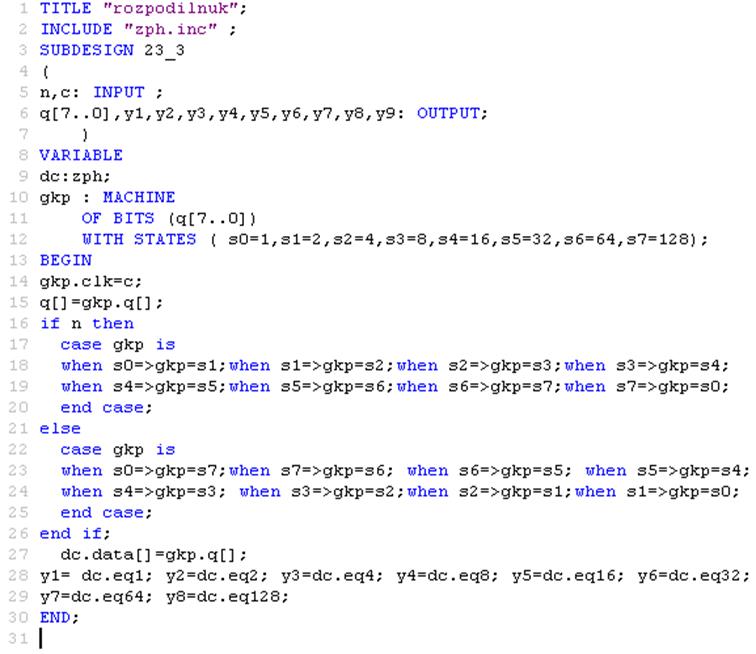

Реалізація розподільника імпульсів на 8 каналів (згідно з варіантом):

Проектування пристрою у графічному редакторі Quartus II:

Як видно із наведених часових діаграм спроектований розподільник імпульсів працює правильно, час затримки сигналу складає близько 7 ns.

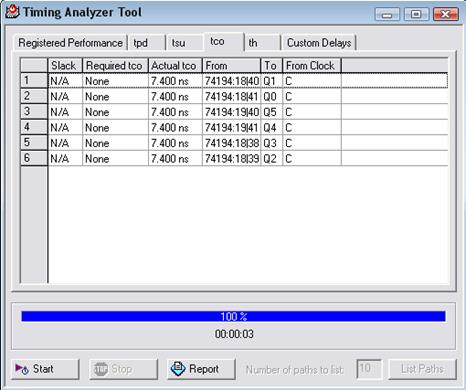

Також наведемо часовий аналіз виконаний за допомогою дисплея Timing Analyzer Tool:

В результаті виконання часового аналізу видно, що затримка складає 7.4 ns):

3.4 Виконати п. 3.3 на тому самому або вищому структурному рівні у текстовому редакторі Quartus II (з іншою назвою проекту, що містить варіант XX).

Виконаємо поставлене завдання у текстовому редакторі Quartus II

Отримані часові діаграми роботи пристрою виконаного у текстовому редакторі Quartus II на структурному рівні, повністю збігаються з попередніми.

Регістрами називаються ЦПП, що виконують операції запису (приймання, введення), збереження, перетворення (наприклад, шляхом зсуву) та зчитування (передавання, виведення) двійкових багатоцифрових чисел (слів). Особливістю регістрів є регулярність їх структури: кожний розряд складається з однакових тригера і додаткових елементів керування розрядом. Через це розрядність регістрів легко нарощується в програмованих ІС або з’єднанням кількох ІС жорсткої структури.

Висновок: В даній частині курсової роботи мною було засвоєно роботу регістрів зсуву на основі яких було створено реверсивний розподільник імпульсів і рівнів, та було засвоєно їх проектування в графічному та текстовому редакторі Quartus II.

4 Виконати вправи з арифметичних основ ЦП

4.1 Виконати алгебричне додавання чисел Х10 з використанням доповняльного, оберненого та двійково-десяткового коду 8421.

-25 - 78

-78 -25

Хпр. = 1.1001110 Хпр.= 1.11001

Хоб = 1.0110001 Хоб = 1.00110

Хдоп = 1.0110010 Хдоп = 1.00111

Хдоп Хоб

![]() 1.0110010

1.0110001

1.0110010

1.0110001

1. 00111 1. 00110

![]()

![]()

![]() 11.0011001

11.0001000

11.0011001

11.0001000

![]()

![]()

![]()

![]()

![]()

1.0011000

-25 X10 доп. Х2/10

-78

1.75![]() 1.0111 0101

1.0111 0101

![]()

![]()

![]() -103

1.22 1.0010 0010

-103

1.22 1.0010 0010

![]() 11.97 10.1000 1010

11.97 10.1000 1010

![]() Х10 пр. =1.03 0110 0110

Х10 пр. =1.03 0110 0110

![]()

![]() 1 1.1001 0111

1 1.1001 0111

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.