Лабораторная работа № 4

«Моделирование процессора дискретного преобразования Фурье»

При моделировании систем может возникнуть неудобство с размещением модели на рабочем столе. Модель может получиться громоздкой и трудно читаемой. Пакет VisSim предоставляет возможность пользователю объединять блоки, вводя составной блок под своим именем. Это делается командой Create Compound Block. Кроме того, модель становится более компактной и при использовании векторного представления величин, когда требуется проводить над ними однообразные процедуры.

Предлагается смоделировать многоканальную систему в виде процессора дискретного преобразования Фурье, k-й выход которого описывается следующей формулой:

=

Scos(k) – jSsin(k),

=

Scos(k) – jSsin(k),

где x(n) – входная последовательность, N – длина последовательности, k=0…N-1 – номер спектральной составляющей.

Этот спектр является комплексным. Амплитудный спектр определится как модуль этого выражения

ПОСЛЕДОВАТЕЛЬНОСТЬ ВЫПОЛНЕНИЯ РАБОТЫ

|

1. Моделирование блока входной памяти 1.1 Собрать схему преобразования входной последовательности сигнала в вектор согласно рисунку 1. Примечание: выход каждой линии задержки соединяется с соответствующим входом блока scalarToVec, последний восьмой вход блока scalarToVec соединяется с блоком wirePositioner Описание блоков приведено в таблице 1 |

Рисунок 1 – преобразователь входной последовательности в вектор |

Таблица 1

|

|

блок генерации сигнала постоянного уровня, чтобы изменить значение константы, необходимо щелкнуть клавишей мыши по блоку: дважды левой или один раз правой Blocks->Signal Producer->const |

|

|

блок задержки сигнала, на вход «t» подается величина задержки, вход «x» – сигнальный Blocks->Time Delay->timeDelay |

|

|

преобразователь набора скалярных сигналов в векторный сигнал, Blocks->Annotation->scalarToVec чтобы добавить или удалить вход, необходимо воспользоваться соответственно командами Edit->Add Connector или Edit->Remove Connector |

|

|

соединитель Blocks->Annotation->wirePositioner |

|

1.2 Выделить полученную схему и сгруппировать схему, выбрав команду Edit>Create Compound Block. В диалоговом окне вписать имя блока “InMem” и нажать кнопку «ОК». Вид получившегося блока должен соответствовать рисунку 2. Чтобы разгруппировать блок, необходимо выбрать команду Edit->Dissolve Compound Block. Чтобы войти внутрь блока, необходимо щелкнуть клавишей мыши по блоку: дважды левой или один раз правой. |

Рисунок 2 – блок памяти |

. Моделирование блока генерации вектора индексов

2.1. Собрать схему согласно рисунку 3, используемые блоки аналогичны описанным в таблице 1. Для ускорения работы рекомендуется один раз поставить блок константы, а затем размножить эти блоки, пользуясь клавишами Ctrl+C (копировать) и Ctrl+V (вставить). Блок scalarToVec можно скопировать из предыдущего блока «InMem».

2.2. Аналогично п. 1.2. сгруппировать данную схему в блок и присвоить ему имя «Index0…7», вид получившегося блока должен соответствовать рисунку 4.

|

Рисунок 3 – схема генерации вектора индексов |

Рисунок 4 – блок генерации вектора индексов |

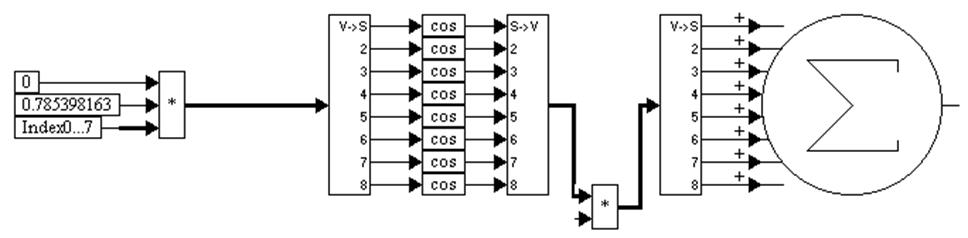

3. Моделирование реальной части одного частотного канала

3.1. Используя стандартные, а также ранее использованные и собранные блоки, собрать схему согласно рисунку 5. Для размножения однотипных блоков рекомендуется пользоваться клавишами Ctrl+C (копировать) и Ctrl+V (вставить). Ранее не описанные блоки указаны в таблице 2

Рисунок 5 – схема реальной части одного частотного канала

Таблица 2

|

|

перемножители, Blocks->Arithmetic->* чтобы добавить или удалить вход, необходимо воспользоваться соответственно командами Edit->Add Connector или Edit->Remove Connector |

|

|

преобразователь векторного сигнала в набор скалярных сигналов, Blocks->Annotation->vecToScalar чтобы добавить или удалить вход, необходимо воспользоваться соответственно командами Edit->Add Connector или Edit->Remove Connector |

|

|

функция cos(x) от входного сигнала, Blocks->Transcendental->cos |

|

|

сумматор, Blocks->Arithmetic->summingJunction чтобы добавить или удалить вход, необходимо воспользоваться соответственно командами Edit->Add Connector или Edit->Remove Connector, для изменения знака входящего слагаемого необходимо щелкнуть по соответствующему входу правой клавишей мыши |

3.2. Аналогично п. 1.2. сгруппировать данную схему в блок и присвоить ему имя «Channel», вид получившегося блока должен соответствовать рисунку 6.

![]()

Рисунок 6 – Блок частотного канала

4. Моделирование действительной части ДПФ восьмого порядка

4.1. Пользуясь клавишами Ctrl+C (копировать) и Ctrl+V (вставить), размножить полученный в п. 3.2. блок «Channel», добавить стандартный блок «соединитель» (Blocks->Annotation->wirePositioner) и преобразователь набора скалярных сигналов в вектор (Blocks->Annotation->scalarToVec) и построить схему, показанную на рисунке 7. Внутри каждого блока, начиная со второго сверху, изменить значение константы «0» на значения «1», «2»,…,«7».

4.2. Сгруппировать данную схему в блок и присвоить ему имя «DFTcos8», вид получившегося блока должен соответствовать рисунку 8.

|

Рисунок 7 – схема реальной части ДПФ |

Рисунок 8 – блок реальной части ДПФ |

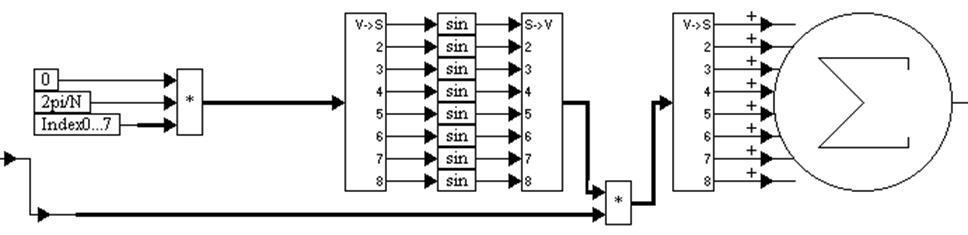

5. Моделирование мнимой части ДПФ восьмого порядка

5.1. Скопировать первый канал из полученного в п. 4.2 блока «DFTcos8» с помощью клавиши Ctrl+C (копировать) и вставить его на свободное поле с помощью клавиши Ctrl+V (вставить).

5.2. Внутри канала заменить все блоки «cos» на блоки «sin» (Blocks->Transcendental->sin), получив схему, представленную на рисунке 9.

Рисунок 9 – схема мнимой части одного частотного канала

5.3. Аналогично п. 4.1 пользуясь клавишами Ctrl+C (копировать) и Ctrl+V (вставить), размножить полученный в п. 5.2. блок «Channel», добавить стандартный блок «соединитель» (Blocks->Annotation->wirePositioner) и преобразователь набора скалярных сигналов в вектор (Blocks->Annotation->scalarToVec) и построить схему, показанную на рисунке 10. Внутри каждого блока, начиная со второго сверху, изменить значение константы «0» на значения «1», «2»,…,«7».

5.4. Сгруппировать данную схему в блок и присвоить ему имя «DFTsin8», вид получившегося блока должен соответствовать рисунку 11.

|

Рисунок 10 – схема мнимой части ДПФ |

Рисунок 8 – блок мнимой части ДПФ |

6. Моделирование блока объединителя квадратур для получения амплитудного спектра

6.1. Используя стандартные блоки, построить схему согласно рисунку 11. Блок извлечения квадратного корня взять из меню Blocks->Transcendental->sqrt.

6.2. Сгруппировать данную схему в блок и присвоить ему имя «BOK», вид получившегося блока должен соответствовать рисунку 12.

|

Рисунок 11 – схема объединителя квадратур |

Рисунок 12 – блок объединителя квадратур |

7. Моделирование процессора ДПФ восьмого порядка

7.1. Используя ранее собранные блоки, а также стандартный блок «соединитель» (Blocks->Annotation->wirePositioner), построить схему согласно рис. 13.

7.2. Сгруппировать данную схему в блок и присвоить ему имя «DFT8», вид получившегося блока должен соответствовать рисунку 14.

|

Рисунок 13 – схема процессора ДПФ восьмого порядка |

Рисунок 14 – блок процессора ДПФ восьмого порядка |

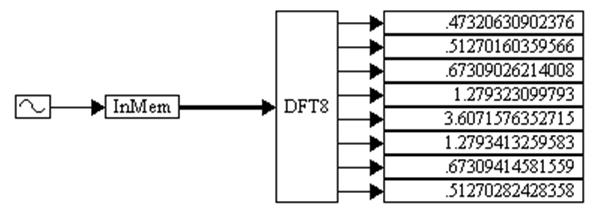

8. Моделирование системы обработки сигнала

8.1. Собрать систему многоканальной обработки сигнала в соответствии с рисунком 15. Ранее не описанные блоки приведены в таблице 3. Частоту синусоиды Frequency (Rad/Sec) взять равной номеру бригады.

Рисунок 15 – система обработки сигнала

Таблица 3

|

|

генератор гармонического сигнала, Blocks->Signal Producer->sinusoid |

|

|

блок отображения значения сигнала, Blocks->Signal Consumer->display |

Для наблюдения входного процесса вывести на рабочий стол осциллограф (Plot) и подсоединить к нему выход блока sinusoid. Так как в модели используются только отсчеты синусоиды, то осциллограф целесообразно поставить в режим Point plot, но при этом точки просматриваются плохо, поэтому можно установить режим Discrete plot. Для индикации отсчетов входного процесса выход блока InMem через блок vecToScalar подсоединить к восьмиканальному блоку отображения сигнала. Последний скопировать с уже созданного.

8.2. Задать значения параметров моделирования в меню Simulate->Simulation Setup равными следующим значениям: Range Start – 0, Step Size – 1, Range End – 7. Запустить процесс моделирования клавишей F5.

8.3. Проверить соответствие полученных значений сигнала в каждом канале расчетным значениям.

Контрольные вопросы

1. Пояснить работу преобразователя

входной последовательности в вектор (Рис. 1).

2. Описать последовательность операций, проводимых при

создании блока InMem (По

рисункам 1 и 2)

3. Пояснить, как составляется схема реальной части одного частотного канала (Рис. 5)

4. Как использовались команды Copy, Paste и Add Connector при моделировании реальной части одного частотного канала?

5. Какие операции использовались при моделировании мнимой части одного частотного канала (Рис. 9)?

6. Зачем нужен блок объединения квадратур? Пояснить, как составлена схема объединителя квадратур.

7. Почему параметры моделирования выбраны следующими: начало (Start) – 0, шаг (Step Size) – 1, конец (End) – 7?

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.