При одновременном ошибочном нажатии двух клавиш клавиатуры, данный триггер вводит в компьютер код только одной из них.

Приоритетные триггеры позволяют предотвратить сбои и ошибки в работе различных устройств.

6 JK-триггер

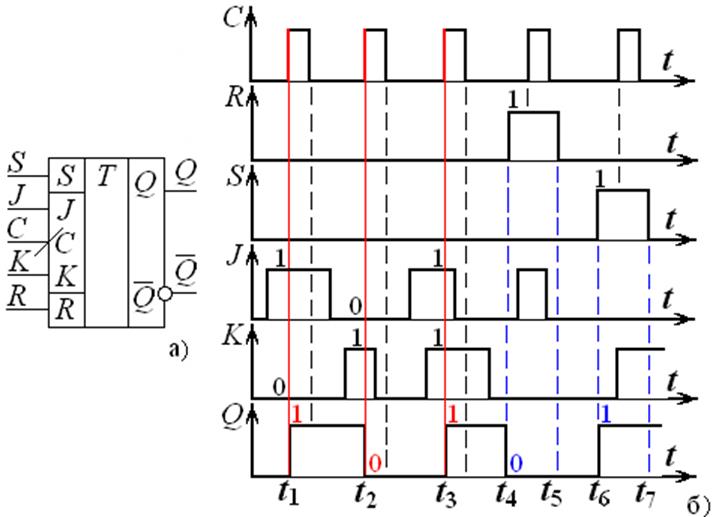

JK-триггер имеет два информационных входа J и K, тактовый динамический вход C, и два приоритетных асинхронных входа установки S и сброса R (рис. 11).

Рис. 11 JK-триггер:

а – принципиальная схема; б – временные диаграммы работы

В таблице истинности триггера (табл. 9) значком «Х» обозначаются произвольные значения переменных J, K и C, которые не оказывают влияния на результат вследствие приоритета входов R, S (моменты времени t4, t5, t6, t7). Этим же определяется нестабильность при R = S = 1, т.к. схема работает как асинхронный RS-триггер.

В случае еслиR = S = 0, асинхронный триггер переходит в режим хранения и разрешается работа синхронного динамического JK-триггера. Запись информации происходит, для данной схемы триггера, по переднему фронту (0-1) сигнала на входе C (моменты времени t1,t2, t3).

Когда на входах J=K=1, происходит инверсия предыдущего значения на выходах триггера (момент времени t3).

Таблица истинности JK-триггера Таблица 9

|

№ |

R |

S |

C |

J |

K |

Q n+1 |

|

1 |

0 |

0 |

0-1 |

0 |

0 |

Q n |

|

2 |

0 |

0 |

0-1 |

0 |

1 |

0 |

|

3 |

0 |

0 |

0-1 |

1 |

0 |

1 |

|

4 |

0 |

0 |

0-1 |

1 |

1 |

Q n’ |

|

5 |

0 |

0 |

1-0 |

X |

X |

Q n |

|

6 |

0 |

0 |

0 |

X |

X |

Q n |

|

7 |

0 |

1 |

X |

X |

X |

1 |

|

8 |

1 |

0 |

X |

X |

X |

0 |

|

9 |

1 |

1 |

X |

X |

X |

– |

Если построить полную таблицу истинности JK-триггера, то можно получить аналитическое выражение его работы:

7 Преобразование триггеров

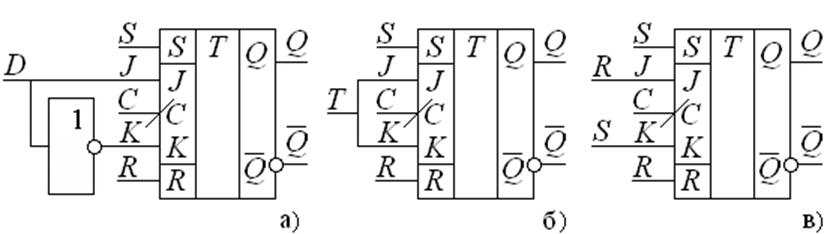

Различные триггеры могут выполнять одинаковые функции за счет использования дополнительных связей. На основе JK-триггера можно получить любой другой триггер, например, синхронные D-триггер, T-триггер, RS–триггер с динамическими входами C (рис. 12, а, б, в).

Рис. 12 Синхронные триггеры с динамическими входами:

а – D-триггер, б –T-триггер, в –RS–триггер

8 MS-триггеры

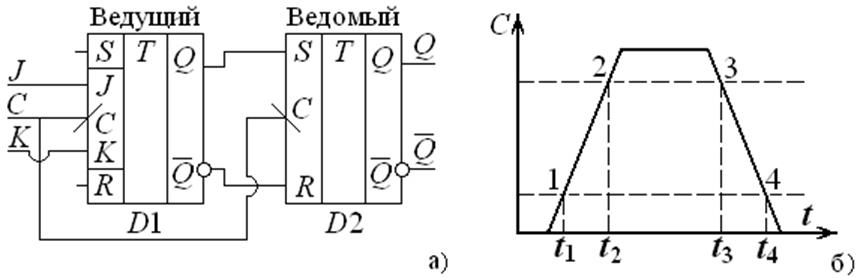

По принципу построения различают одноступенчатые триггеры, рассмотренные выше, и двухступенчатые триггеры. Последние состоят из двух ячеек памяти – последовательно включенных триггеров (рис. 13). Триггер D1 имеет тактовый вход C, который реагирует на передний фронт импульса синхронизации C, а входы триггера D2 реагирует на задний фронт этого импульса. Вначале информация записывается в первую ступеньD1, а затем переписывается во вторую D2 и появляется на выходе.

Двухступенчатый триггер обозначается вместо символа T символами TT, управляется по обоим фронтам, реализуются по схеме «ведущий-ведомый» (вход C как у D1).

Рис. 13 MS-триггер:

а – принципиальная схема; б – временные диаграммы работы

Последовательность работы MS-триггера:

- на интервале времени t1 – t2 ведущий триггер D1 сохраняет поступающую в него информацию, ведомый триггер D2 отключен от D1;

- на интервале времени t2 – t3 оба триггера отключены;

- на интервале времени t3 – t4 ведущий триггер D1 отключен от информационных сигналов, ведомый триггерD2 сохраняет поступающую в него информацию от D1.

Двухступенчатые триггеры могут состоять из собственно триггера и динамической промежуточной ячейки памяти. Они управляются только одним фронтом тактового импульса – передним фронтом из 0 в 1.

Данные MS-триггеры используются в цифровых устройствах, где при поступлении тактового сигнала информация записывается в первый триггер и не должна проходить сразу во все триггеры, подключенные последовательно за первым (регистры).

Чтобы предотвратить такое сквозное прохождение сигнала, для одноступенчатых динамических триггеров нужно использовать импульсы синхронизации с очень крутыми (короткими по времени) фронтами.

Тогда благодаря задержке переключения первого триггера, подключенный к нему триггер успеет перейти в режим хранения до поступления на его вход новой информации, т.к. сигнал на тактовом входе, общий для всех триггеров, уже успеет переключиться в постоянное значение и отключит этот триггер.

Триггеры с MS структурой являются динамическими. Для исключения сбоев в работе, у этих триггеров нормируется минимально допустимый промежуток времени до появления фронта сигнала C, когда на входе данные не должны изменяться.

Также указывается аналогичный интервал – время удержания данных, после завершения фронта тактового импульса.

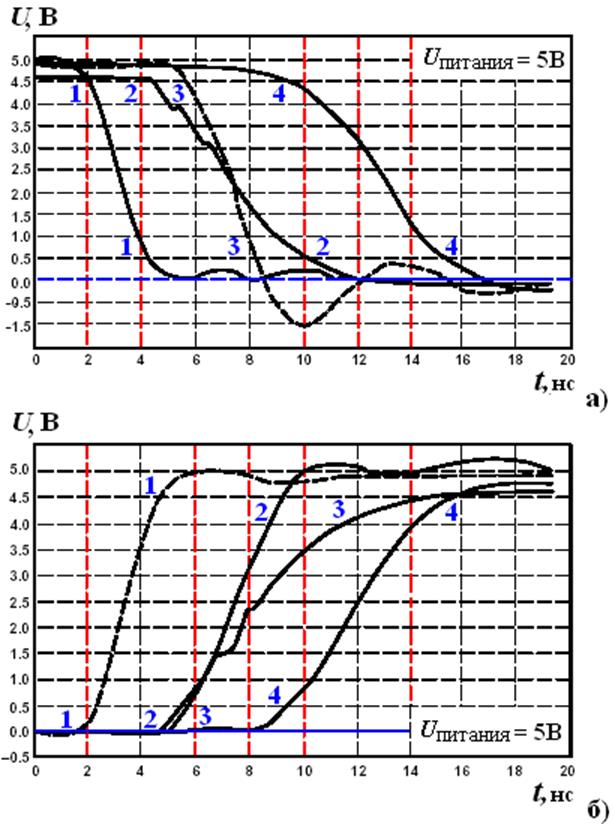

На рисунке 14 представлены временные диаграммы передних и задних фронтов переключений различных типов логических элементов, полученные экспериментально.

Рис. 14 Графики фронтов цифровых сигналов: а – заднего; б - переднего

На логические элементы, изготовленные по различной технологии, одновременно поступает входной сигнал в момент времени t =0 и начинается их переключение. График 1 соответствует эмиттерно-связанной логике (ЭСЛ); график 2: транзисторно-транзисторной логике с диодами Шотки (ТТЛШ); график 3: транзисторно-транзисторной логике (ТТЛ); график 4: логике на комплементарных полевых транзисторах метал-окисел-полупроводник (КМОП). Из временных диаграмм следует, что всякое переключение логических элементов сопровождается переходным процессом. Если тактовый сигнал появится во время, пока этот процесс не закончился, то возможна ошибка считывания информации.

9 Разработка триггеров

Для разработки схем триггеров используется следующий алгоритм:

Составляется полная таблица истинности, из которой получают аналитическое выражение работы триггера.

Выбирается тип базового триггера (бистабильной ячейки, рис. 4, а; 5, а) и записывается его характеристическое уравнение.

На основе сравнения таблицы истинности разрабатываемого триггера и его аналитического выражения выбирают дополнительные логические элементы, составляют требуемую схему.

Выводы

Триггеры являются ячейками памяти, куда заносится информация в двоичном коде, при необходимости информация считывается.

Совмещая в себе функциональные возможности более простых видов триггеров, JK-триггер является универсальным.

Динамическая работа триггеров позволяет снизить вероятность влияния помех при считывании информации из-за сокращения временного интервала записи. Это свойство используется в сложных цифровых устройствах.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.