Лекция 3

Преобразователи кодов

3.1 Дешифраторы и шифраторы

Шифрирование это способ сжатия данных, дешифрирование – обратное преобразование. Условные обозначения дешифраторов и шифраторов DC и CD (decoder и coder соответственно).

3.1.1 Дешифраторы

Дешифратор преобразует двоичный код на его нескольких входах в сигнал только на одном выходе. Если назначение дешифратора преобразование из двоичного в десятичный код, то номер выхода равен десятичному эквиваленту двоичного кода.

Дешифраторы обычно используются для формирования адреса устройства при обмене данными между ним и микропроцессором, области хранения информации, наименования команды микропроцессора, как часть больших интегральных схем, кроме того, для выбора одного из нескольких внешних устройств.

В полном дешифраторе CD(n-m) количество выходов m = 2n, где n - число входов.

В неполных дешифраторах DC m < 2n (для преобразования BIN→BCD). Они могут применяться для управления, например, индикаторами (микросхема К155ИД1 CD(4-10)).

Активный сигнал на прямых входах/выходах 1, на инверсных входах/выходах - 0.

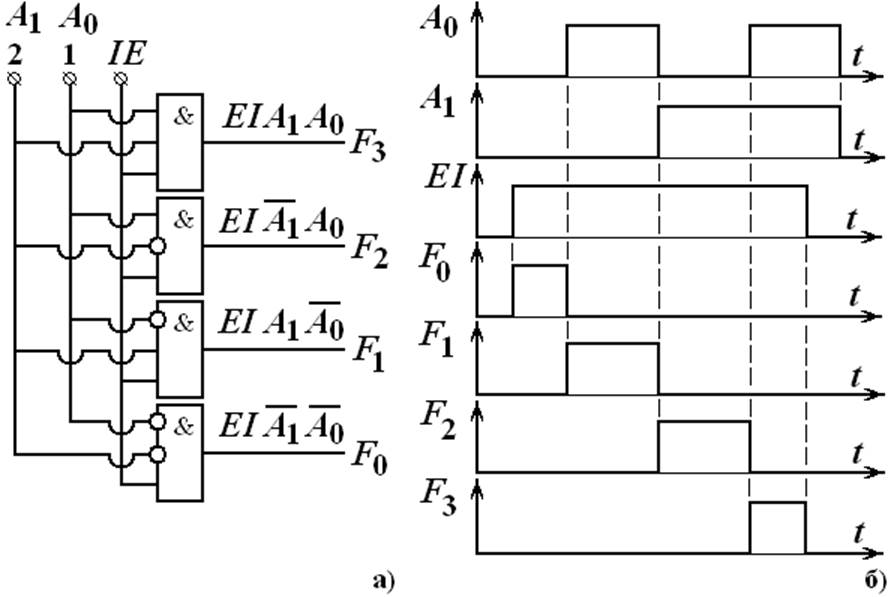

Рассмотрим DC (2 – 4) с n = 2, m = 4 и входом разрешения выходов 0E.

Дешифратор является частным случаем демультиплексора и может быть получен из последнего за счет исключения информационного входа и использования адресных входов в качестве информационных.

Схема дешифратора на четыре выхода приведена на рис. 3.1. Поведение дешифратора описывается таблицей истинности (табл. 3.1).

Кроме информационных входов у шифраторов обычно имеются служебные входы:

Служебный вход EI (V) или его инверсия (EI’) используется для разрешения работы дешифратора в определенный интервал времени при условии EI =1 (стробирование).

Кроме того, вход EI может применяться в качестве информационного входа, если дешифратор работает как демультиплексор и передает сигнал с EI на один из выходов в соответствии данными на адресных (информационных) входах.

Также вход EI позволяет увеличивать разрядность дешифратора за счет использования нескольких DC в одном преобразователе.

Таблица истинности DC (2-4) Таблица 3.1

|

№ |

N10 |

Входы |

Выходы |

|||||

|

Служебный |

Адресные |

|||||||

|

EI |

A1 |

A0 |

F3 |

F2 |

F1 |

F0 |

||

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

|

2 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

|

3 |

2 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

|

4 |

3 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

|

5 |

X |

0 |

X |

X |

0 |

0 |

0 |

0 |

Дешифраторы выпускаются, как правило, в виде микросхем с количеством выходов 4, 8, 10, 16, 32. Ряд микросхем имеют инверсные выходы, например, К555ИД3.

Рис. 3.1 Схема дешифратора CD (2-4) а,

и временная диаграмма его работы, б.

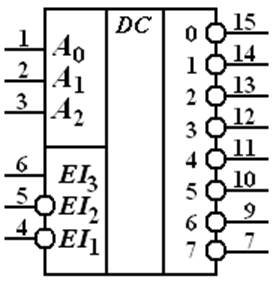

Пример. Характеристики и обозначение микросхемы К555ИД7.

Это двоично-десятичный дешифратор – демультиплексор, преобразующий трехразрядный код A0...A2 в напряжение низкого уровня (логический ноль), появляющееся на одном из восьми выходов 0...7. Микросхема выполнена в пластмассовом корпусе 238.16-2 с двухрядным вертикальным расположением выводов.

Электрические параметры микросхемы К555ИД7 приведены в табл.3.1, условное графическое обозначение на рис.3.2, назначение выводов в таблице истинности 3.2.

Параметры К555ИД7

Таблица 3.1

Параметры К555ИД7

Таблица 3.1

|

Uпит., ном., В |

5 |

|

U0вых., не более, В |

0.48 |

|

U1вых., не менее, В |

2.9 |

|

I0вх., не более, мА |

-0.36 |

|

I1вх., не более, мА |

0.02 |

|

Iпот., не более, мА |

10 |

|

t1.0зд.р., не более, нс |

41 |

|

t0.1зд.р., не более, нс |

27 |

Рис. 3.2Обозначение

микросхемы К555ИД7

Согласно структурной схеме дешифратор на основании входного трехразрядного двоичного кода должен устанавливать логический ноль на одном из восьми выходов.

Если микросхема используется как демультиплексор, дешифратор может принимать по входам ЕIпрямой (ЕI3), а также инверсный (ЕI1, ЕI2) адресные коды. Состояния при дешифрации кода А0, А1, А2 и демультиплексировании по адресу А0, А1, А2 представлены в табл. 3.2.

Таблица истинности дешифратора К555ИД7 Таблица 3.2

|

№ |

Входы |

Выходы |

|||||||||||||

|

Служебные |

Информационные |

Информационные |

|||||||||||||

|

/EI1 |

/EI2 |

EI3 |

A0 |

A1 |

A2 |

/0 |

/1 |

/2 |

/3 |

/0 |

/1 |

/2 |

/3 |

||

|

/0 |

/1 |

/2 |

/3 |

/4 |

/5 |

/6 |

/7 |

||||||||

|

1 |

1 |

X |

X |

X |

X |

X |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

2 |

X |

1 |

X |

X |

X |

X |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

3 |

X |

X |

0 |

X |

X |

X |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

4 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

5 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

6 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

|

|

7 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

|

|

8 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

|

|

9 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

|

|

10 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

|

11 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

Примечание: значком «/» обозначается инверсия.

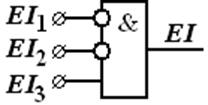

Служебные входы внутри микросхемы объединены (рис. 3.3) в соответствии с выражением:

|

Рис. 3.3 Служебные входы CD

Это позволяет расширить функциональные возможности дешифратора.

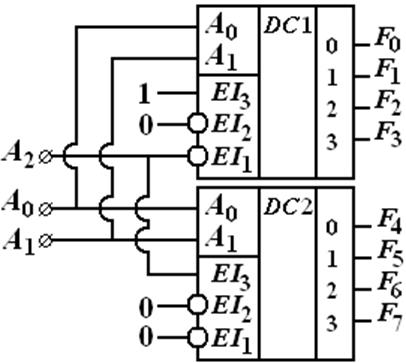

Увеличение разрядности дешифратора

Для расширения возможностей применения дешифраторов возможно увеличение их разрядности за счет объединения нескольких микросхем (рис. 3.4). Работа дешифратора CD (3-8) основывается на уравнении (3.1) и поясняется таблицей истинности (3.3).

Рис. 3.4 Увеличение разрядности дешифратора

|

(3.1)

Расширение разрядности DC(2-4) до DC(3-8) Таблица 3.3

|

№ |

Входы |

Выходы |

||||||||||||

|

Сл-е |

Информационные |

Информационные |

||||||||||||

|

/EI2 |

A1 |

A0 |

EI1 |

EI3 |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

||

|

DC 1 |

DC 2 |

|||||||||||||

|

1 |

1 |

X |

X |

X |

X |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

2 |

X |

Х |

Х |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

3 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

4 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

5 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

|

6 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

|

7 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

|

8 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

|

9 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

|

10 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

Примечание: значком «/» обозначается инверсия.Значения EI1 приведены с учетом инверсии.

Старший разряд A3 используется для управления работой дешифраторов с помощью служебных входов EI1 и EI3.

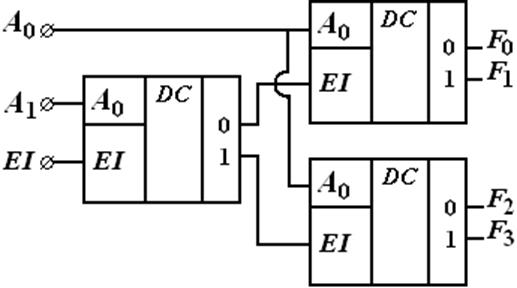

Старшие разряды двоичного числа могут быть поданы на дешифратор, который преобразует их в сигналы разрешения EI для других дешифраторов, которые преобразуют младшие разряды. Это позволяет увеличить разрядность дешифратора (рис. 3.5).

Рис. 3.5 Увеличение разрядности дешифратора

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.