Лабораторная работа 4.3. Запоминающие устройства

Цель работы. Изучение схем запоминающих устройстви их функционирования.

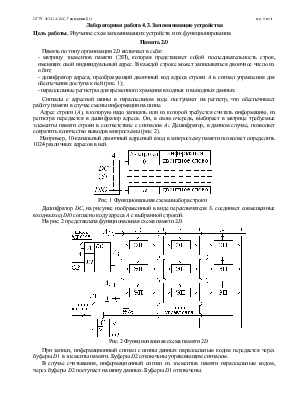

Память 2D

Память по типу организации 2D включает в себя:

- матрицу элементов памяти (ЭП), которая представляет собой последовательность строк, имеющих свой индивидуальный адрес. В каждой строке может записываться двоичное число из n бит;

- дешифратор адреса, преобразующий двоичный код адреса строки A в сигнал управления для обеспечения доступа к ней (рис. 1);

- параллельные регистры для временного хранения входных и выходных данных.

Сигналы с адресной шины в параллельном коде поступают на регистр, что обеспечивает работу памяти в случае смены информации на шине.

Адрес строки (A), в которую надо записать или из которой требуется считать информацию, из регистра передается в дешифратор адреса. Он, в свою очередь, выбирает в матрице требуемые элементы памяти строки в соответствие с сигналом Ai. Дешифратор, в данном случае, позволяет сократить количество выводов микросхемы (рис. 2).

Например, 10-канальный двоичный адресный вход в микросхему памяти позволяет определить 1024 различных адресов в ней.

Рис. 1 Функциональная схема выбора строки

Дешифратор DC, на рисунке изображенный в виде переключателя S, соединяет совмещенные вход-выход DI0 согласно коду адреса A с выбранной строкой.

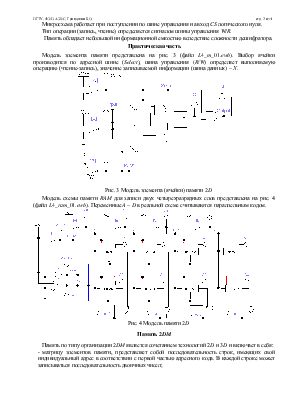

На рис. 2 представлена функциональная схема памяти 2D.

Рис. 2 Функциональная схема памяти 2D

При записи, информационный сигнал с шины данных параллельным кодом передается через буферы D1 в элементы памяти. Буферы D2 отключены управляющим сигналом.

В случае считывания, информационный сигнал из элементов памяти параллельным кодом, через буферы D2 поступает на шину данных. Буферы D1 отключены.

Микросхема работает при поступлении по шине управления на вход CS логического нуля.

Тип операции (запись, чтение) определяется сигналом шины управления W/R.

Память обладает небольшой информационной емкостью вследствие сложности дешифратора.

Практическая часть

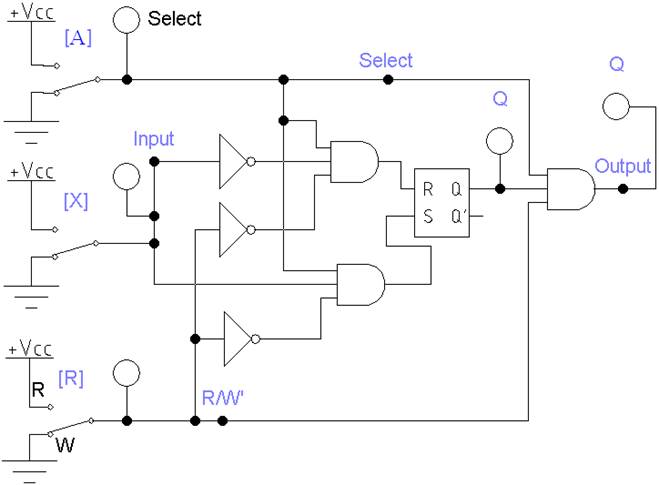

Модель элемента памяти представлена на рис. 3 (файл L4_m_01.ewb). Выбор ячейки производится по адресной шине (Select), шина управления (R/W) определяет выполняемую операцию (чтение-запись), значение записываемой информации (шина данных) – Х.

Рис. 3 Модель элемента (ячейки) памяти 2D

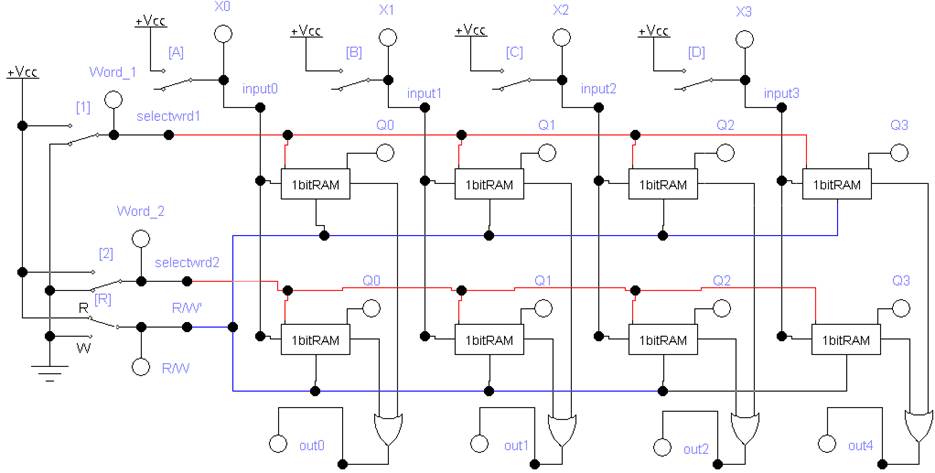

Модель схемы памяти RAM для записи двух четырехразрядных слов представлена на рис. 4 (файл L4_ram_01.ewb). Переменные A – D в реальной схеме считываются параллельным кодом.

Рис. 4 Модель памяти 2D

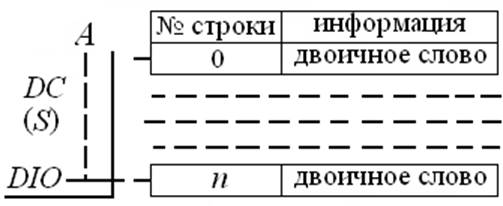

Память 2DM

Память по типу организации 2DM является сочетанием технологий 2D и 3D и включает в себя:

- матрицу элементов памяти, представляет собой последовательность строк, имеющих свой индивидуальный адрес в соответствии с первой частью адресного кода. В каждой строке может записываться последовательность двоичных чисел;

- дешифратор адреса X, преобразующий первую часть двоичного кода адреса в сигнал управления, для организации доступа к выбранной строке матрицы;

-мультиплексоры, которые выбирают необходимые элементы памяти из строк согласно второй части адресного кода;

- дешифратор адреса Y, управляющий работой мультиплексоров.

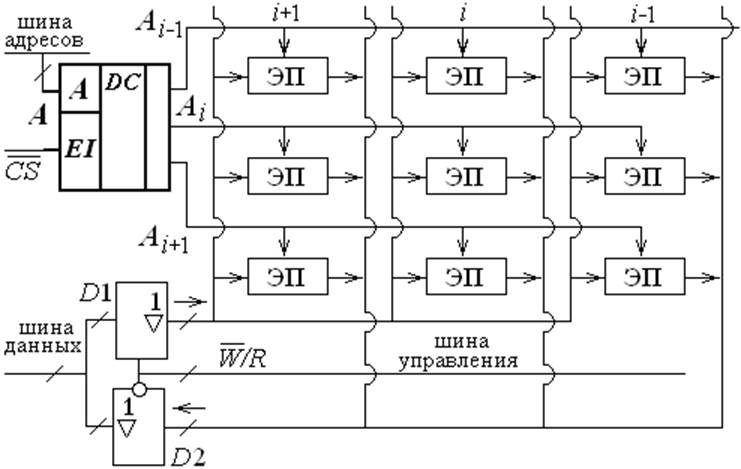

Принцип работы памяти:

Дешифратор X выбирает строки, каждая из которых содержит группы элементов памяти, равные по информационной емкости.

Первая группа предназначена для первых разрядов слов, размещенных в строке, вторая группа – для вторых разрядов и т.д.

Дешифратор Y вырабатывает сигнал управления, согласно которому мультиплексоры считывают из каждой группы по одному разряду двоичного слова.

Например, дешифратор X, в соответствии с адресом, выбирает седьмую строку. Согласно сигналу управления дешифратора Y, мультиплексоры во всех группах этой строки обращаются к четвертому элементу памяти. Из первой группы первый мультиплексор считывает первый разряд слова, из второй группы второй мультиплексор – второй разряд и. т.д.

Операция записи информации происходит аналогично.

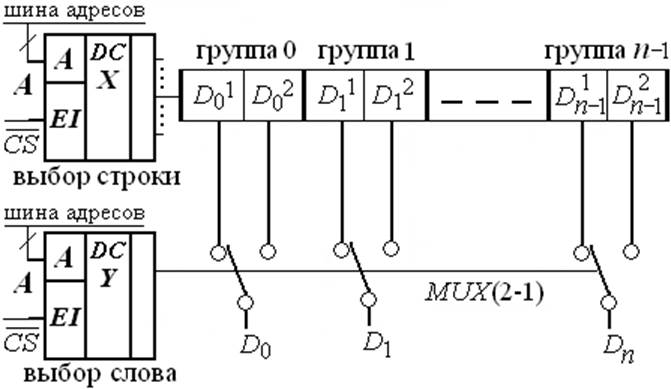

На рисунке 5 представлена часть схемы памяти, каждая строка которой содержит два двоичных n – разрядных числа, первое слово: D01…D n-11, второе слово: D02…D n-12.

По данному алгоритму создается память большой информационной емкости, т.к. она состоит из несложных отдельных элементов.

Рис. 5 Часть функциональной схемы памяти 2DM

Практическая часть

Задание 1

Изучить работу элементов памяти (файлы L4_m_00.ewb, L4_m_01.ewb, L4_ram_01.ewb, L4_ram_02.ewb, L4_ram_03.ewb, L4_ram_04.ewb), определить логические сигналы на их выходах.

Задание 2

Заполнить таблицу истинности (табл. 1) для ячейки памяти, файл L4_m_01.ewb, в соответствии с указанными операциями в столбце Примечание.

Таблица задания 2 Таблица 1

|

A |

X |

R |

Q |

Output |

Примечание |

|

С ячейкой обмена информацией нет |

|||||

|

Запись в ячейку логической единицы |

|||||

|

Считывание из ячейки логической единицы |

|||||

|

Запись в ячейку логического нуля |

|||||

|

Считывание из ячейки логического нуля |

Использовать обозначения:Q n– предыдущее значение на выходе триггера;

X – любое значение переменной, которое не оказывает влияния на результат.

Задание 3

Заполнить таблицу истинности (табл. 2) для модели памяти 2D, файл L4_ram_01.ewb, в соответствии с указанными операциями в столбце Примечание.

Таблица задания 3 Таблица 2

|

Word2 |

Word1 |

R |

D |

C |

B |

A |

Out3 |

Out2 |

Out1 |

Out0 |

Примечание |

|

нет обмена информацией |

|||||||||||

|

Запись Word 1: 1100 |

|||||||||||

|

Считывание Word 1: 1100 |

|||||||||||

|

Запись Word 2: 0111 |

|||||||||||

|

Считывание Word 2: 0111 |

Задание 4

Заполнить таблицу истинности (табл. 3) для модели памяти 2DM, файл L4_ram_03.ewb, в соответствии с указанными операциями в столбце Примечание.

Таблица задания 4 Таблица 3

|

R |

D |

C |

B |

A |

Line |

S |

OutQ1 |

OutQ0 |

Примечание |

|

нет обмена информацией |

|||||||||

|

Запись Word 1: 01 |

|||||||||

|

Считывание Word 1: 01 |

|||||||||

|

Запись Word 2: 10 |

|||||||||

|

Считывание Word 2: 10 |

Задание 5

Заполнить таблицу истинности (табл. 4) для модели памяти 2DM, файл L4_ram_04.ewb, в соответствии с указанными операциями в столбце Примечание.

Таблица задания 3 Таблица 4

|

Line2 |

Line1 |

R |

D |

C |

B |

A |

S |

OutQ1 |

OutQ0 |

Примечание |

|

нет обмена информацией |

||||||||||

|

Запись Word 2: 01 |

||||||||||

|

Считывание Word 2: 01 |

||||||||||

|

Запись Word 4: 10 |

||||||||||

|

Считывание Word 4: 10 |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.