Лабораторная работа 3.2

JK-триггеры

Цель работы

Изучение различных схем JK-триггеров и их функционирования, приобретение навыков в определении характеристик триггеров.

Основные теоретические положения

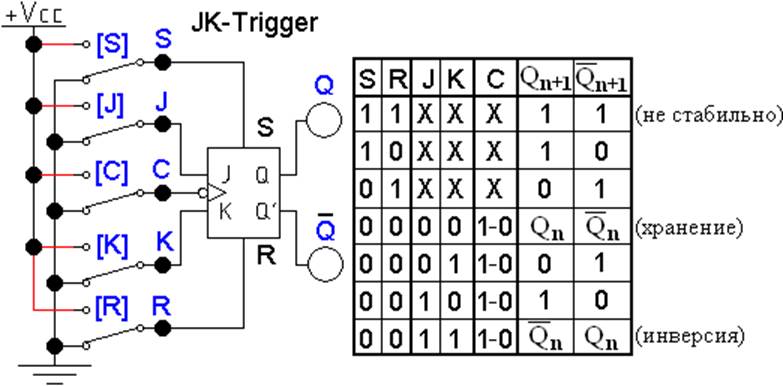

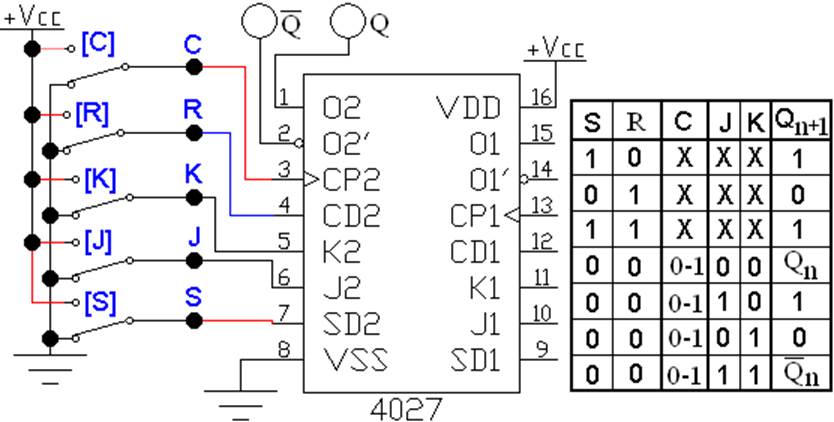

Схема JK-триггера и таблица истинности представлены на рис. 1. Файлы для моделирования JK-триггеров расположены в папке Lab_3_2\Модели.

JK-триггер имеет два информационных входа J и K, тактовый динамический вход C, и два приоритетных асинхронных входа установки S и сброса R.

Рис. 1 JK-триггер из поля элементов Digital

Значком «Х» обозначаются произвольные значения переменных J, K и C, которые не оказывают влияния на результат вследствие приоритета входов R, S. Этим же определяется нестабильность при R=S=1, т.к. схема работает как асинхронный RS-триггер.

триггер имеет вход установки “0” (R - вход) и вход установки “1” (S - вход).

В случае еслиR=S=0, асинхронный триггер переходит в режим хранения и разрешается работа синхронного динамического JK-триггера. Запись информации происходит при переходе из состояния 1 в состояние 0 сигнала на входе C.

Когда на входах J=K=1, происходит инверсия предыдущего значения на выходах триггера.

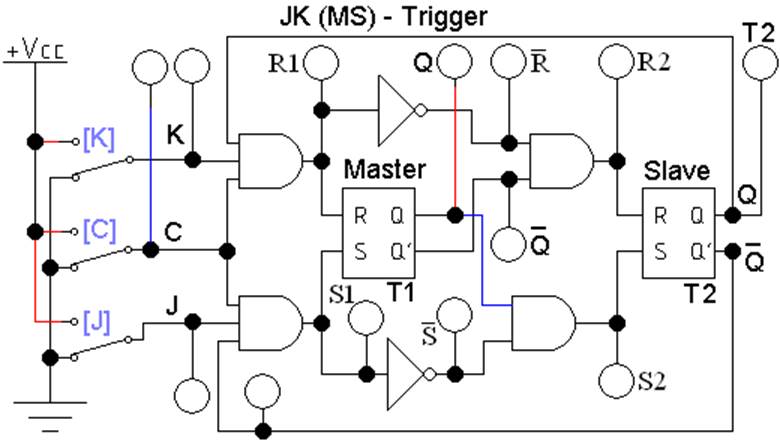

1 MS-триггеры

Двухступенчатые триггеры состоят из двух ячеек памяти – последовательно включенных триггеров (рис. 2). Триггер T1 имеет тактовый вход, который реагирует на передний фронт импульса сигнала синхронизации C. Управляемый схемой запрета (элементы «И», «НЕ»), вход триггера T2 реагирует на задний фронт импульса сигнала синхронизации.

Следовательно, двухступенчатый триггер управляется по обоим фронтам, и реализуются по схеме «ведущий-ведомый».

Рис. 2 MS-триггер

Обозначение Триггера с переключением по заднему фронту C – значок инверсии и треугольник, направленный острым углом внутрь микросхемы.

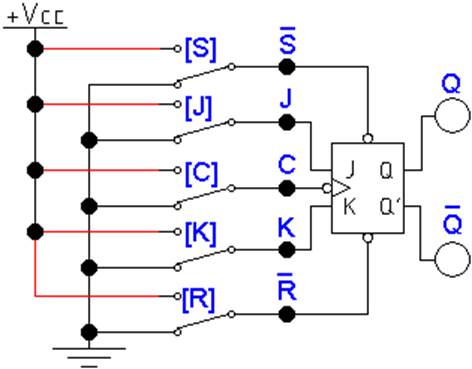

На рисунке 3 представлена схема двухступенчатой схемы JK-триггера с инверсными входами R и S.

Рис. 3 JK-триггер из поля элементов Digital

Двухступенчатые триггеры могут состоять из собственно триггера и динамической промежуточной ячейки памяти. Они управляются только одним фронтом тактового импульса – передним фронтом из 0 в 1.

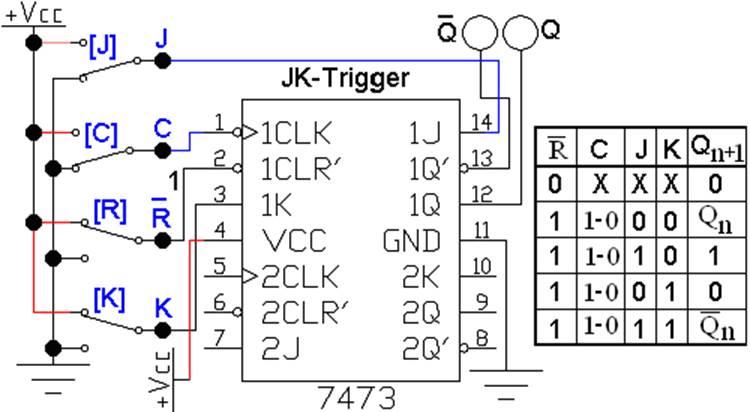

На рисунке 4 изображен такой триггер, обозначение его динамического входа C – треугольник, направленный острым углом внутрь микросхемы.

Питание микросхемы 7473 обеспечивается источником +5В, включенным относительно нулевого вывода GND (земля). У триггера имеется один установочный вход R (инверсный), для приоритетной установки выхода Q =0.

Микросхема содержит два JK-триггера, для анализа работы используется только один.

Рис. 4 JK-триггер из поля элементов Digital

Динамический триггер на микросхеме 4027 с двумя установочными входами и его таблица истинности представлены на рис. 5.

Микросхема также содержит два JK-триггера, для анализа работы используется только один.

Рис. 5 JK-триггер из поля элементов Digital

Задание 1.

Определить логические сигналы на прямом и инверсном выходе триггера, файл L3_JK_01.ewb.

Задание 2.

Заполнить таблицы истинности (табл. 1, 2) MS – триггера (показывает принцип работы JK-триггера) и JK-триггера соответственно, файлы L3_JK_02.ewb, L3_JK_03.ewb.

Таблица задания 2 Таблица 1 Таблица 2

|

№ |

J |

K |

C |

T1 |

T2 Qn+1 |

S’ |

R’ |

J |

K |

C |

Qn+1 |

|

|

1 |

1 |

0 |

0-1 |

0 |

0 |

Х |

Х |

Х |

||||

|

2 |

1 |

0 |

1-0 |

0 |

1 |

Х |

Х |

Х |

||||

|

3 |

0 |

1 |

0-1 |

1 |

0 |

Х |

Х |

Х |

||||

|

4 |

0 |

1 |

1-0 |

1 |

1 |

0 |

0 |

0-1 или 1-0 |

||||

|

5 |

0 |

0 |

0-1 |

1 |

1 |

1 |

0 |

|||||

|

6 |

0 |

0 |

1-0 |

1 |

1 |

0 |

1 |

|||||

|

7 |

1 |

1 |

0-1 |

1 |

1 |

1 |

1 |

|||||

|

8 |

1 |

1 |

1-0 |

В таблице использовать: T1 – выход Q ведущего триггера (на выход MS – триггера не поступает). T2 – выход Q ведомого триггера (поступает на выход MS – триггера). S’,R’, Q n’ – инверсные значения S, R, Q n. В столбце Qn+1 использовать символы: 0, 1, Q n, Q n’. Переключение по переднему фронту обозначать 0 – 1, по заднему: 1 – 0, что соответствует изменению сигнала от низкого значения до высокого значения и наоборот соответственно. Запрещенное состояние – запрет.

Внимание. Исследование моделей начинать при T1 = T2 =0 и последовательно с 1 по 8 строку таблицы. С подачи R, S, затем J, K сигналов, а уже потом сигнала С, исключив излишние переключения во избежание путаницы в ответах.

Задание 3.

Заполнить таблицу истинности (табл. 3, 4) триггеров, файлы L3_JK_04.ewb, L3_JK_05.ewb, микросхемы 7473 и 4027 в своем составе имеют два JK триггера.

Таблица задания 3 Таблица 3 Таблица 4

|

R’ |

J |

K |

C |

Qn+1 |

S |

R |

J |

K |

C |

Qn+1 |

|

|

Х |

Х |

Х |

1 |

1 |

Х |

Х |

Х |

||||

|

Q n |

0 |

1 |

Х |

Х |

Х |

||||||

|

0 |

1 |

0 |

Х |

Х |

Х |

||||||

|

1 |

Q n |

||||||||||

|

Q n’ |

0 |

||||||||||

|

1 |

|||||||||||

|

Q n’ |

Задание 4.

Письменно ответить на следующие вопросы (на обратной стороне листа):

– в чем главное отличие работы триггеров Задания 2, табл. 2 и Задания 3, табл. 4?

– какой из них можно применять в регистрах с последовательной записью (используется последовательный код) и почему?

Выводы. Совмещая в себе функциональные возможности нескольких более простых видов триггеров, JK-триггер является универсальным.

Динамическая работа триггеров позволяет снизить вероятность влияния помех при считывании информации из-за сокращения временного интервала записи. Также это свойство используется в более сложных устройствах, куда входят JK-триггеры.

Данные триггеры обычно являются MS – триггерами, что важно, например, при создании на их основе устройства задержки передачи сигнала на фиксированное время.

Область применения, например, в регистрах с последовательной записью и (или) считыванием (последовательный код).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.