Лабораторная работа 3.3

D-триггер

Цель работы

Изучение различных схем D-триггера и их функционирования, приобретение навыков в определении характеристик триггеров.

Основные теоретические положения

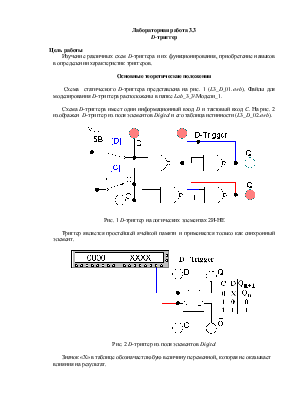

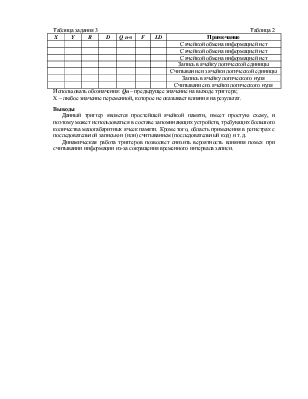

Схема статического D-триггера представлена на рис. 1 (L3_D_01.ewb). Файлы для моделирования D-триггера расположены в папке Lab_3_3\Модели_1.

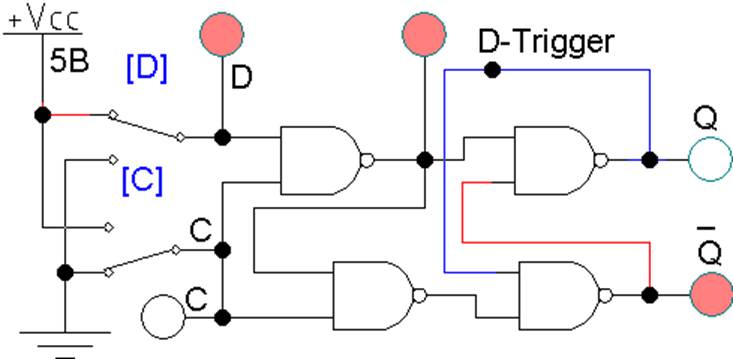

Схема D-триггера имеет один информационный вход D и тактовый вход C. На рис. 2 изображен D-триггер из поля элементов Digital и его таблица истинности (L3_D_02.ewb).

Рис. 1 D-триггер на логических элементах 2И-НЕ

Триггер является простейшей ячейкой памяти и применяется только как синхронный элемент.

Рис. 2 D-триггер из поля элементов Digital

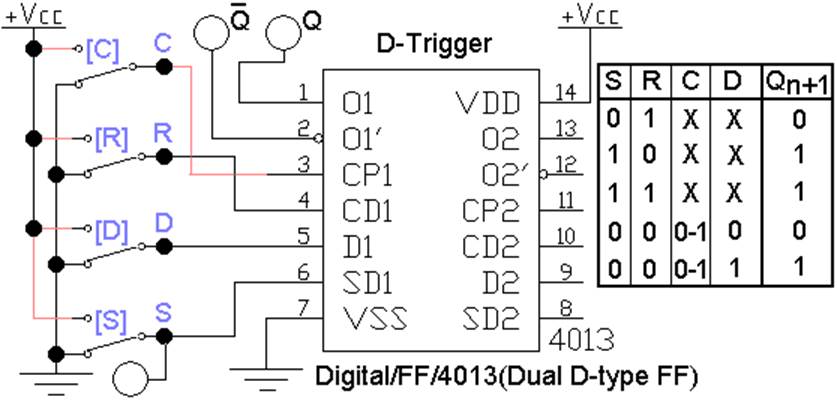

Значок «Х» в таблице обозначает любую величину переменной, которая не оказывает влияния на результат.

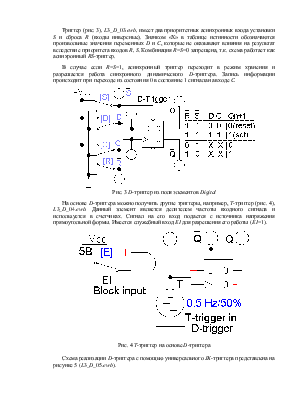

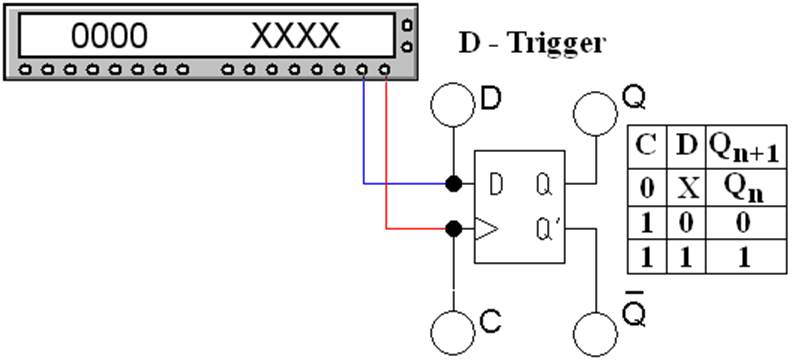

Триггер (рис. 3), L3_D_03.ewb, имеет два приоритетных асинхронных входа установки S и сброса R (входы инверсные). Значком «Х» в таблице истинности обозначаются произвольные значения переменных D и C, которые не оказывают влияния на результат вследствие приоритета входов R, S. Комбинация R=S=0 запрещена, т.к. схема работает как асинхронный RS-триггер.

В случае еслиR=S=1, асинхронный триггер переходит в режим хранения и разрешается работа синхронного динамического D-триггера. Запись информации происходит при переходе из состояния 0 в состояние 1 сигнала на входе C.

Рис. 3 D-триггер из поля элементов Digital

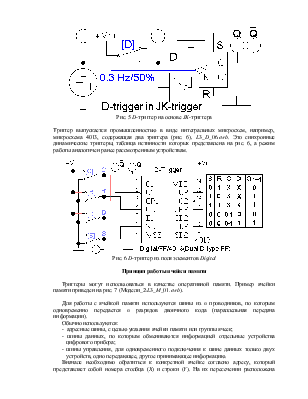

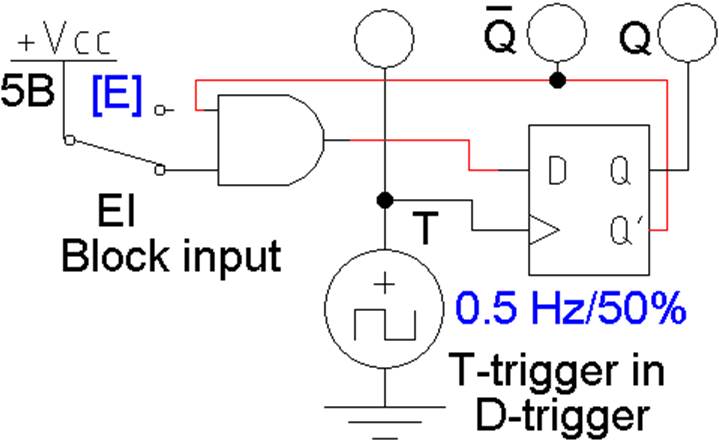

На основе D-триггера можно получить другие триггеры, например, T-триггер (рис. 4), L3_D_04.ewb. Данный элемент является делителем частоты входного сигнала и используется в счетчиках. Сигнал на его вход подается с источника напряжения прямоугольной формы. Имеется служебный вход EI для разрешения его работы (E I=1).

Рис. 4 T-триггер на основе D-триггера

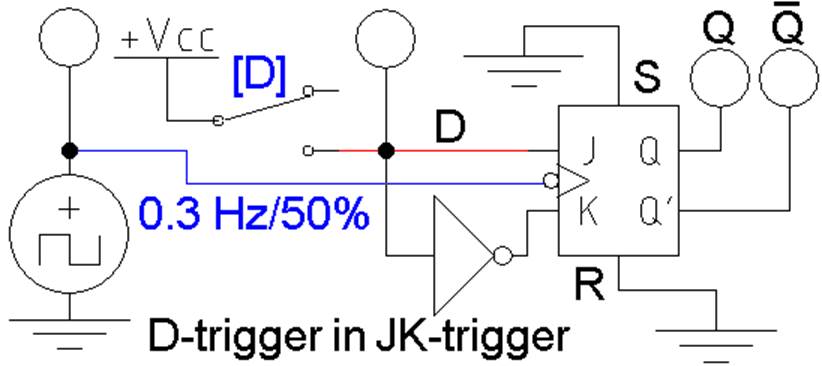

Схема реализации D-триггера с помощью универсального JK-триггера представлена на рисунке 5 (L3_D_05.ewb).

Рис. 5 D-триггер на основе JK-триггера

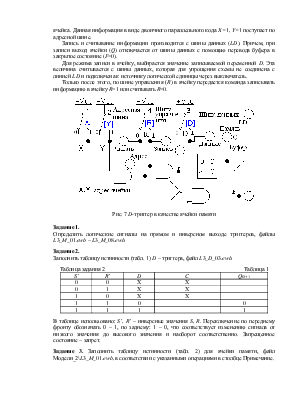

Триггер выпускается промышленностью в виде интегральных микросхем, например, микросхема 4013, содержащая два триггера (рис. 6), L3_D_06.ewb. Это синхронные динамические триггеры, таблица истинности которых представлена на рис. 6, а режим работы аналогичен ранее рассмотренным устройствам.

Рис. 6 D-триггер из поля элементов Digital

Принцип работы ячейки памяти

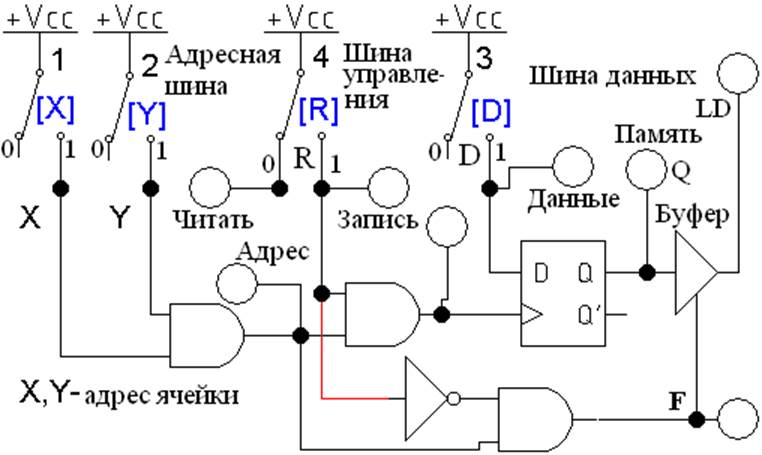

Триггеры могут использоваться в качестве оперативной памяти. Пример ячейки памяти приведен на рис. 7 (Модели_2\L3_M_01.ewb).

Для работы с ячейкой памяти используются шины из n проводников, по которым одновременно передается n разрядов двоичного кода (параллельная передача информации).

Обычно используются:

- адресные шины, с целью указания ячейки памяти или группы ячеек;

- шины данных, по которым обмениваются информацией отдельные устройства цифрового прибора;

- шины управления, для одновременного подключения к шине данных только двух устройств, одно передающее, другое принимающее информацию.

Вначале необходимо обратиться к конкретной ячейке согласно адресу, который представляет собой номера столбца (X) и строки (Y). На их пересечении расположена ячейка. Данная информация в виде двоичного параллельного кода X=1, Y=1 поступает по адресной шине.

Запись и считывание информации производится с шины данных (LD). Причем, при записи выход ячейки (Q) отключается от шины данных с помощью перевода буфера в закрытое состояние (F=0).

Для режима записи в ячейку, выбирается значение записываемой переменной D. Эта величина считывается с шины данных, которая для упрощения схемы не соединена с линией LD и подключена к источнику логической единицы через выключатель.

Только после этого, по шине управления (R) в ячейку передается команда записывать информацию в ячейку R=1 или считывать R=0.

Рис. 7 D-триггер в качестве ячейки памяти

Задание 1.

Определить логические сигналы на прямом и инверсном выходе триггеров, файлы L3_M_01.ewb – L3_M_08.ewb.

Задание 2.

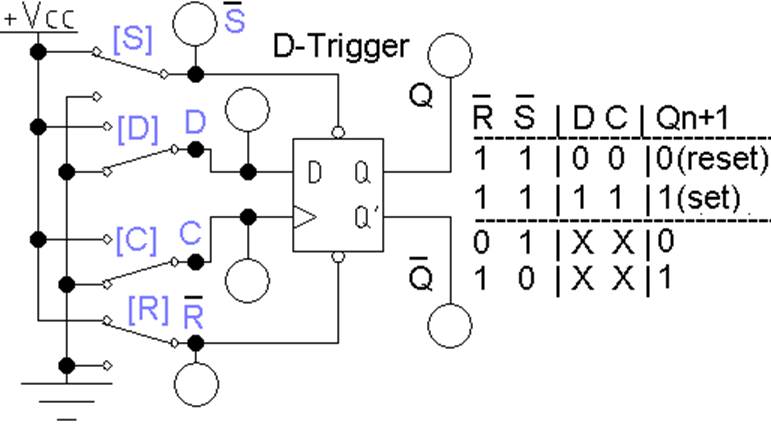

Заполнить таблицу истинности (табл. 1) D – триггера, файл L3_D_03.ewb.

Таблица задания 2 Таблица 1

|

S’ |

R’ |

D |

C |

Qn+1 |

|

0 |

0 |

Х |

Х |

|

|

0 |

1 |

Х |

Х |

|

|

1 |

0 |

Х |

Х |

|

|

1 |

1 |

0 |

0 |

|

|

1 |

1 |

1 |

1 |

В таблице использовано: S’, R’ – инверсные значения S, R.Переключение по переднему фронту обозначать 0 – 1, по заднему: 1 – 0, что соответствует изменению сигнала от низкого значения до высокого значения и наоборот соответственно. Запрещенное состояние – запрет.

Задание 3. Заполнить таблицу истинности (табл. 2) для ячейки памяти, файл Модели_2\L3_M_01.ewb, в соответствии с указанными операциями в столбце Примечание.

Таблица задания 3 Таблица 2

|

X |

Y |

R |

D |

Q n+1 |

F |

LD |

Примечание |

|

С ячейкой обмена информацией нет |

|||||||

|

С ячейкой обмена информацией нет |

|||||||

|

С ячейкой обмена информацией нет |

|||||||

|

Запись в ячейку логической единицы |

|||||||

|

Считывание из ячейки логической единицы |

|||||||

|

Запись в ячейку логического нуля |

|||||||

|

Считывание из ячейки логического нуля |

Использовать обозначения:Q n– предыдущее значение на выходе триггера;

X – любое значение переменной, которое не оказывает влияния на результат.

Выводы

Данный триггер является простейшей ячейкой памяти, имеет простую схему, и поэтому может использоваться в составе запоминающих устройств, требующих большого количества малогабаритных ячеек памяти. Кроме того, область применения в регистрах с последовательной записью и (или) считыванием (последовательный код) и т. д.

Динамическая работа триггеров позволяет снизить вероятность влияния помех при считывании информации из-за сокращения временного интервала записи.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.