МИНИСТЕРСТВО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

Государственное образовательное учреждение

ВПО «Уральский государственный технический университет – УПИ»

Кафедра «Радиоэлектронные и телекоммуникационные системы»

Логический элемент «И-НЕ» (ТТЛ)

Исследование комбинационных логических схем

Лабораторная работа № 1

Ф.И.О.

Преподаватель Маевская Е. А.

Студент Емельянов А. Ю.

Группа р 35071

Екатеринбург 2007

Цель работы

Ознакомиться с аппаратурой, входящей в лабораторную установку, изучить лабораторный стенд и его возможности. Определить среднее время запаздывания схемы «И-НЕ». Экспериментально исследовать комбинационные логические схемы (КЛС). Оценить быстродействие КЛС.

Схема для определения среднего времени запаздывания (4 элемента И-НЕ):

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

|

|

|

|

|

Половина периода сигнала на выходе счетчика:

Схема с 6-ю элементами И-НЕ:

![]()

![]()

![]()

|

Половина периода сигнала на выходе счетчика:

Среднее время запаздывания одного элемента:

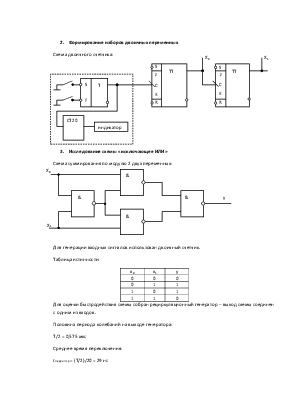

2. Формирование наборов двоичных переменных

|

|

|

|

3. Исследование схемы «исключающее ИЛИ»

|

|

Схема суммирования по модулю 2 двух

переменных:

Схема суммирования по модулю 2 двух

переменных:

Для генерации входных сигналов использован двоичный счетчик.

Таблица истинности:

|

x0 |

x1 |

y |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Для оценки быстродействия схемы собран рециркуляционный генератор – выход схемы соединен с одним из входов.

Половина периода колебаний на выходе генератора:

Т/2 = 0,575 мкс

Среднее время переключения:

τперекл ср = (Т/2)/20 = 29 нс

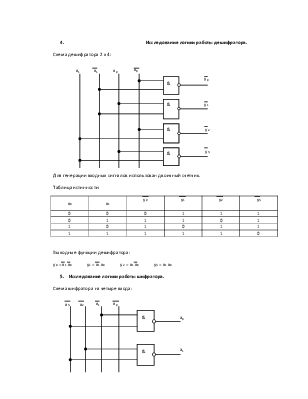

4. Исследование логики работы дешифратора.

Схема дешифратора 2 х 4:

|

Для генерации входных сигналов использован двоичный счетчик.

Таблица истинности:

|

x0 |

x1 |

|

|

|

|

|

0 |

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

1 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

1 |

1 |

0 |

Выходные функции дешифратора:

![]()

![]()

![]()

![]() y0 = x1 x0 y1

= x1 x0 y2 = x1 x0

y3 = x1 x0

y0 = x1 x0 y1

= x1 x0 y2 = x1 x0

y3 = x1 x0

5. Исследование логики работы шифратора.

Схема шифратора на четыре входа:

|

![]()

![]() Логические функции

для формирования разрядов двоичного кода:

Логические функции

для формирования разрядов двоичного кода:

![]()

![]() а0 = х1

х3 а1 = х2 х3

а0 = х1

х3 а1 = х2 х3

Таблица истинности:

|

х3 |

х2 |

х1 |

х0 |

а1 |

а0 |

|

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

1 |

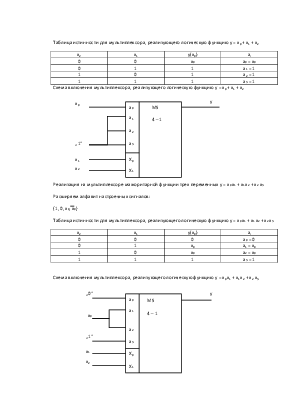

6. Исследование логики работы мультиплексора

![]()

![]()

|

|

|

|

Таблица истинности мультиплексора в режиме переключателя каналов:

|

z1 |

z0 |

y |

|

0 |

0 |

x0 |

|

0 |

1 |

x1 |

|

1 |

0 |

x2 |

|

1 |

1 |

x3 |

Мультиплексор в режиме универсального логического модуля.

Реализация на мультиплексоре логической функции y = x0 + x1 + x2

Расширяем алфавит настроечных сигналов:

![]() {1, 0, x0,

x0}

{1, 0, x0,

x0}

Таблица истинности для мультиплексора, реализующего логическую функцию y = x0 + x1 + x2

|

х2 |

х1 |

у(х0) |

аi |

|

0 |

0 |

х0 |

а0 = х0 |

|

0 |

1 |

1 |

а1 = 1 |

|

1 |

0 |

1 |

а2 = 1 |

|

1 |

1 |

1 |

а3 = 1 |

|

|

Реализация на мультиплексоре мажоритарной функции трех переменных y = x0 х1 + x1 х2 + x2 х3

Расширяем алфавит настроечных сигналов:

![]() {1, 0, x0,

x0}

{1, 0, x0,

x0}

Таблица истинности для мультиплексора, реализующего логическую функцию y = x0 х1 + x1 х2 + x2 х3

|

х2 |

х1 |

у(х0) |

аi |

|

0 |

0 |

0 |

а0 = 0 |

|

0 |

1 |

х0 |

а1 = х0 |

|

1 |

0 |

х0 |

а2 = х0 |

|

1 |

1 |

1 |

а3 = 1 |

Схема включения мультиплексора, реализующего логическую функцию y = x0 х1 + x1 х2 + x2 х3

|

|

|

|

|

|||||

Выводы по работе

В ходе проведения лабораторной работы были исследованы логический элемент «И-НЕ» и комбинационные логические схемы.

Было определено среднее время запаздывания элемента «И-НЕ», для чего были измерены половины периодов сигналов на выходе рециркуляционных генераторов на трех элементах и на пяти элементах.

Был собран и исследован двоичный счетчик для формирования наборов двоичных переменных и проверена его работа.

Собрана и исследована схема «исключающее ИЛИ», определена ее таблица истинности с помощью двоичного счетчика и оценено быстродействие схемы. При x1 = 0 схема ведет себя по отношению к х0 как повторитель, а при х1 =1 – как инвертор.

Собран и исследован дешифратор 2 х 4, с помощью двоичного счетчика получена его таблица истинности и выходные функции.

Проведено исследование логики работы дешифратора на четыре входа. Построены его таблицы истинности.

Была исследована логика работы мультиплексора как переключателя каналов, получена его таблица истинности, а также как универсального логического модуля, для чего на мультиплексоре были реализованы логические функции y = x0 + x1 + x2 и y = x0 х1 + x1 х2 + x2 х3. При работе мультиплексора в режиме УЛМ назначение его входов меняется: адресные входы становятся информационными, а те, что были информационными, становятся настроечными. Для настройки мультиплексора был расширен алфавит настроечных сигналов – одна из информационных переменных перенесена в число настроечных.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.