Цифровая электроника оперирует электрическими эквивалентами цифр. При этом числа чаще всего представляются в двоичной системе, в которой существуют только два знака: единица и нуль, им соответствуют сигналы «логическая единица» и «логический нуль», которые для краткости будем обозначать просто 1 и 0.

В XIX в. ирландским математиком Булем с целью перевода логических доказательств на язык математики были разработаны основы алгебры логики, названной впоследствии булевой алгеброй.

Основное понятие булевой алгебры – переключательная (булева) функция. Ее аргументы (переменные) и она сама могут принимать только два значения: 0 и 1. Оказалось, что с помощью булевых функций можно описать действие целого класса схем цифровой электроники, а также правила функционирования сочетаний этих схем. Такого рода схемы называются комбинационными, так как сигнал на их выходе (1 или 0) определяется комбинацией сигналов (единиц и нулей) на их входах.

В булевой алгебре доказана теорема: функция любого количества переменных может быть получена методом суперпозиции из функций двух переменных. Метод суперпозиции заключается в подстановке на место переменных других булевых функций и (или) перенумерации переменных, т.е. в их перестановке. Теорема и пояснение сущности метода суперпозиции позволяют ограничиться рассмотрением булевых функций только двух переменных и строить многовходовые комбинационные схемы только из двухвходовых схем. При этом необходимо, чтобы выходы одних схем можно было подключить ко входам других.

Набор функций двух переменных, из которого методом суперпозиции можно получить любые булевы функции называется функционально полным набором.

Набор исходных схем или логических элементов, реально используемых в цифровой электронике, описывается избыточно полным функциональным набором булевых функций. Избыточность набора позволяет получить несколько вариантов одинаково функционирующих схем и выбрать из них те, которые лучше подходят для решения конкретных задач.

Примеры электрических схем, реализующих наиболее употребительные в цифровой электронике булевы функции, приведены на рис. 6.1. Эти схемы, к сожалению, не удовлетворяют требованию возможности включения выходов одних на входы других, но они наглядны.

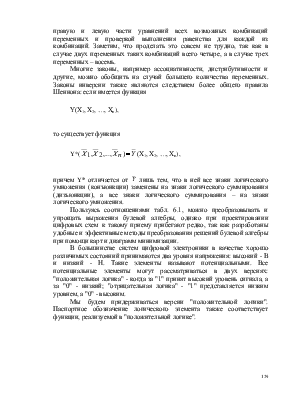

Основные правила и теоремы булевой алгебры приведены в табл. 6.1.Убедиться в их справедливости нетрудно методом подстановки в правую и левую части уравнений всех возможных комбинаций переменных и проверкой выполнения равенства для каждой из комбинаций. Заметим, что проделать это совсем не трудно, так как в случае двух переменных таких комбинаций всего четыре, а в случае трех переменных – восемь.

Многие законы, например ассоциативности, дистрибутивности и другие, можно обобщить на случай большего количества переменных. Законы инверсии также являются следствием более общего правила Шеннона: если имеется функция

Y(Х1, Х2, …, Хn),

то существует функция

Y*(![]() (Х1, Х2, …, Хn),

(Х1, Х2, …, Хn),

причем

Y* отличается от ![]() лишь

тем, что в ней все знаки логического умножения (конъюнкции) заменены на знаки

логического суммирования (дизъюнкции), а все знаки логического суммирования –

на знаки логического умножения.

лишь

тем, что в ней все знаки логического умножения (конъюнкции) заменены на знаки

логического суммирования (дизъюнкции), а все знаки логического суммирования –

на знаки логического умножения.

Пользуясь соотношениями табл. 6.1, можно преобразовывать и упрощать выражения булевой алгебры, однако при проектировании цифровых схем к такому приему прибегают редко, так как разработаны удобные и эффективные методы преобразования решений булевой алгебры при помощи карт и диаграмм минимизации.

В большинстве систем цифровой электроники в качестве хорошо различимых состояний принимаются два уровня напряжения: высокий - В и низкий - Н. Такие элементы называют потенциальными. Все потенциальные элементы могут рассматриваться в двух версиях: "положительная логика" - когда за "1" принят высокий уровень сигнала, а за "0" - низкий; "отрицательная логика" - "1" представляется низким уровнем, а "0" - высоким.

Мы будем придерживаться версии "положительной логики". Паспортное обозначение логического элемента также соответствует функции, реализуемой в "положительной логике".

Таблица 6.1.

|

А + 0 = А А + 1 = 1 А + А = А А +

В + А = А + В А + А · В = А А +

(А + В) + С = А + (В + + С) = А + В +С А + В · С = (А + В) х х(А + С) |

А · 1 = А А · 0 = 0 А × А = А А × В · А = А · В А · (А + В) = А А · (

(А · В) · С = А · (В · С) = = А · В · С А · (В + С) = А · В + + А · С |

Закон двойного отрицания Закон коммутатив- ности Закон поглощения Законы инверсии (де Моргана) Закон ассоциатив- ности Закон дистрибутив- ности |

Базовые схемы – это схемы элементов, представляющих собой функционально полный набор. Чаще всего – это схемы И-НЕ либо ИЛИ-НЕ, их обычно называют вентилями.

Основной базовый вентиль логических интегральных микросхем (ИМС) транзисторно-транзисторной логики (ТТЛ) выполняет функцию И-НЕ. Схема базового вентиля (рис. 6.2,а) состоит из трех функциональных частей: логическая функция реализуется входным многоэмиттерным транзистором VT1; на транзисторе VT2 построен фазорасщепляющий каскад, в эмиттерную цепь которого включен транзистор VT3, улучшающий переходную характеристику каскада; выходной каскад представляет собой инвертор на транзисторе VT5 с активной коллекторной нагрузкой (VT4), резистор R5 ограничивает броски тока во время переключения. При подаче хотя бы на один из входов напряжения низкого уровня транзистор VT1 входит состояние насыщения, а следовательно транзисторы VT2 и VT5 – в состояние отсечки; выход Y через открытый транзистор VT3 получает напряжение высокого уровня. Когда на все входы вентиля подается напряжение высокого уровня, транзистор VT1 работает в инверсном режиме с малым коэффициентом передачи тока, через резистор R1 получают прямое смещение коллекторный переход транзистора VT1 и эмиттерные переходы транзисторов VT2 и VT5 – выход Y через насыщенный транзистор VT5 получает низкий уровень. Напряжение на коллекторе открытого транзистора VT2 может быть порядка 1 В, поэтому для надежного запирания транзистора VT4 в его эмиттерную цепь включен диод VD3, поднимающий потенциал эмиттера VT4 на 0,7 В. Диоды VD1 и VD2 ограничивают возможные отрицательные выбросы входного напряжения.

На рис. 6.2 приведена шкала напряжений, соответствующих низкому (Н) и высокому (В) стандартным логическим уровням (б), таблица состояний (в) и условное обозначение (г) рассмотренного вентиля.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.