Рис.10

Если же полный набор входов не требуется, то диод и связанный с ним резистор, относящиеся к ненужному входу R или R, удаляют, ненужный вход S соединяют с минусовым проводом питания, а вход S — с плюсовым.

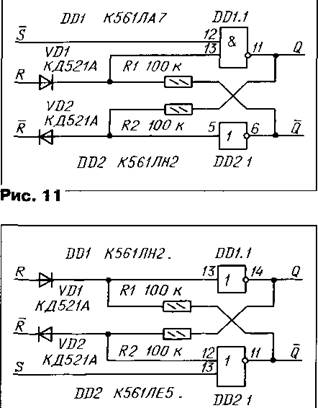

Упрощенные варианты схемы этого триггера представлены на рис. 11—13. Здесь один из логических элементов заменен инвертором Во всех триггерах сопротивление резисторов можно выбирать в пределах от 10 кОм до 1 МОм.

RS-триггеры на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ. Особый интерес представляет возможность реализации RS-триггера на одном элементе исключающее ИЛИ, управляемого по двум входам, о чем свидетельствует публикация [1]. Здесь элемент DD1.1 (см рис 1) в режиме хранения (RT=0) по отношению к верхнему по схеме выходу является повторителем, ОС через

Рис.12

резистор R2 положительна. Подача входного импульса SD=1 при низком уровне на выходе приводит к скачкообразному переходу триггера в единичное состояние. Повторная подача этого импульса не изменяет состояния триггера, входной импульс на выход не проходит. Импульсы "дребезга" триггер подавляет- Таким образом, при переключении в единичное состояние триггер ведет себя как классический.

В этом состоянии на верхнем входе элемента действует высокий уровень в результате действия положительной ОС. После подачи входного импульса RT=1 процесс переключения идет в несколько этапов. Пока амплитуда импульса увеличивается от нуля до примерно Unop, элемент является повторителем, а ОС через резистор — положительна (первая фаза формирования выходного перепада).

При амплитуде, близкой к Uпop, элемент DD1.1 уже и не повторитель, и не инвертор, а цепь ОС оказывается разомкнутой, так как выходное напряжение и дифференциальный коэффициент усиления элемента практически равны нулю независимо от напряжения на втором входе элемента.

После увеличения амплитуды до номинального единичного уровня на обоих входах действует высокий уровень:

на нижнем — входной импульс, на верхнем из-за действия заряженной емкости Со, включающей входную емкость элемента, выходную емкость источника входного импульса SD и емкость монтажа- В результате происходит переключение элемента (вторая фаза формирования выходного перепада). Можно считать, что элемент переключается быстрее, чем подзаряжается емкость Со (с постоянной времени т=СоРос) и выходное напряжение падает до нуля до того. как разрядилась емкость Со.

При достижении RT^1 элемент по отношению к верхнему входу становится инвертором, и по мере разрядки емкости Со напряжение на верхнем входе элемента уменьшается, а на выходе — увеличивается. Замыкается цепь ОС, элемент переходит в аналоговый режим. Напряжение на его выходе и верхнем входе увеличивается до Unop (для элемента микросхемы К561ЛП2

Unop-onu^).

Таким образом, элемент DD1.1 триггера по схеме на рис. 1 из [1] после переключения в нулевое состояние находится в аналоговом режиме и поэтому усиливает сетевые наводки и импульсные помехи либо становится генератором, импульсы "дребезга" при RT=1 проходят на выход с уровнем 0,41-)пит-Этот триггер не отвечает свойствам 1, 2 и 7, сформулированным в начале статьи. Наличие режима отрицательной ОС при действии импульса на входе RT ухудшает помехозащищенность (см. [4]) как самого триггера, так и последующих узлов. При действии запрещенной комбинации SD=RT-1 триггер принимает нулевое состояние.

Некоторые свойства этого триггера можно улучшить. Установлено, что амплитуда паразитного импульса на выходе, по времени совпадающего с импульсом RT=1, зависит от амплитуды установочного импульса на входе RT. Как уже было упомянуто, при RT^Unop амплитуда

паразитного импульса достигает примерно 0,4ипит, при RT=0,67Unop — уже 0,125и„ит, а при RT-0,5Unop — О,

Это свойство элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, кстати, можно использовать для регулировки амплитуды. При изменении управляющего напряжения на выв. 1 (6, 8, 13) от 0 примерно до 0,5Ur,op будет плавно изменяться амплитуда выходного импульса, повторяющего по форме импульс, поданный на выв. 2 (5, 9, 12). При значениях RT<0,5Unop уровень паразитного импульса остается практически равным О, но при этом значительно (в десятки раз) увеличивается время спада выходного импульса.

Таким образом, для установки триггера в нулевое состояние необходимо на вход RT подать импульс половинной амплитуды.

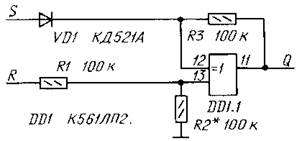

Схема рассмотренного варианта триггера с улучшенными переходными характеристиками изображена на рис. 14. Здесь в цепь входа R включен резистивны и делитель R1.R2. Этот триггер импульсы "дребезга" на входе R подавляет, но спад выходного импульса у него затянут из-за отсутствия положительной ОС во второй фазе формирования выходного импульса (не выполняется свойство 2). Резистор R3 может иметь сопротивление в пределах от 10 кОмдо 1 МОм.

Обратим еще раз внимание на то, что при реализации триггера по рис. 14 на различных элементах микросхемы К561ЛП2 сигнал положительной ОС нужно подавать на входы 2, 5, 9, 12, иначе в вьходном единичном импульсе появится "просечка" (см. выше).

В RS-триггере по схеме на рис. 2* в [1] единичный импульс на вход R поступает через дифференцирующую цепь C1R2, что несколько улучшает переходные характеристики для первого импульса на входе R благодаря укорочению импульса, действующего на вход элемента, однако при повторной подаче импульса на вход R пиковое значение продифференцированного импульса, проходящего на выход триггера, все равно остается близким к 0,41-)пит.

Переходные характеристики этого триггера могут быть существенно улучшены. если "разбить" резистор R2 на две примерно равные части и снимать сигнал на вход элемента со средней их точки, как это сделано на рис. 14.

Несмотря на указанные возможности улучшения переходных характеристик триггеров из [I], не следует забывать, что в них возможен аналоговый режим работы элемента ИСКЛЮЧАЮЩЕЕ

Рис.14

* Примечание редакции. К сожалению, в этой публикации была допущена ошибка при монтаже рисунков: рисунком 2 следует считать рис. 3, а рисунком 3 — рис. 2, В настоящей статье А. Самойленко эта поправка учтена.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.