Отметим, что указанная комбинация сигналов появляется только в одном случае, при чтении информации с АЦП, т.к. система не содержит других ВУ, с которых производилось бы считывание информации.

Буферный регистр 1533ИР33 (DD7), как уже указывалось, служит для выставления на шину данных по сигналу INTA номера вектора прерывания (20h), сформированного на выходе регистра сигналом RESET с микросхемы К1810ГФ84.

Цифро-аналоговый преобразователь К1108ПА1 выполняет функции линейного преобразования 8-ми разрядного параллельного кода в выходной униполярный ток. На выходе микросхемы включен быстродействующий операционный усилитель типа К574УД1, преобразующий выходной ток в напряжение и умощняющий выходной сигнал.

ИС К574УД1 обладает коэффициентом усиления по напряжению KU=5×104, выходным напряжением 10В и скоростью его нарастания 50-100В/мкс. В цепи стабилизации опорного напряжения применен стабилитрон КС191Ф.

Внешние резисторы R1-R4 позволяют регулировать выходное напряжение и напряжение смещения нуля в небольших пределах. Емкость С1 позволяет минимизировать время установления выходного тока.

Микросхема ЦАП К1108ПА1 работает от двух источников питающих напряжений UП1=5В±5%, UП2=15В±5% и от источника опорного напряжения UИОН=10,24В±1%.

ИС ОУ К574УД1 питается от источников UП1=15В±5% и UП2= -15В±5%.

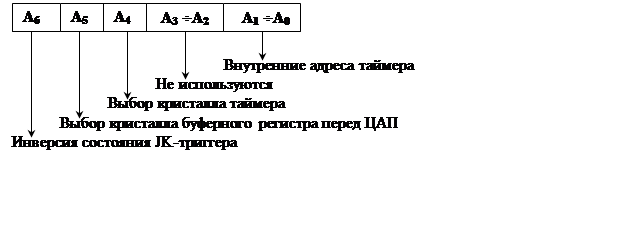

Данные на ЦАП поступают с буферного регистра типа 1533ИР33 (DD10), входной буфер которого открывается сигналом нулевого уровня CS (“выбор кристалла”), формирующимся при M/IO= “1” и A5= “0”.

Передача данных на выход регистра происходит при поступлении уровня лог. 1 на вход EDI микросхемы, в качестве данного сигнала используется инвертированный сигнал (“запись ВУ”), вырабатываемый при M/IO= “1” и WR= “0”.

При превышении выходным информационным сигналом определенного значения обеспечивается включение индуцирующего светодиода, управление которым осуществляется универсальным JK-триггером, выполненном на микросхеме 134ТВ14.

Для этого на системную адресную линию A6 подается уровень лог. 0, который совместно с сигналом M/IO= “1” при помощи схемы И формирует сигнал высокого уровня, подключаемый одновременно к выводам J и K микросхемы, осуществляя инверсию предыдущего состояния триггера.

Установка триггера в исходное состояние происходит по сигналу RESET, подключенному ко входу R (“установка нуля”), тактовые сигналы синхронизации системы PCLK подаются к соответствующему входу триггера С (“синхронизация”).

Программируемый таймер К1810ВИ54, как уже указывалось, генерирует импульсы запуска на АЦП с периодичностью FPCLK/N , где N- загружаемая программно константа пересчета. В работе таймера используется только один 0-й канал, выход которого OUT0 подключен ко входу запуска АЦП. Работа канала во времени определяется тактовыми импульсами PCLK, подаваемыми на вход CLK0, входные адресные линии таймера A0 и A1 подключены к младшим адресным линиям системы, по ним осуществляется адресация к одному из каналов таймера при программировании.

Вход WR используется также при программировании таймера, на него подается системный управляющий сигнал (“запись ВУ”), который ориентирует входной буфер микросхемы на ввод, т.е. ПТ принимает информацию от ЦП.

Работа входного буфера разрешается управляющим сигналом CS (“выбор кристалла”), формирующимся при M/IO= “1” и A4= “0”.

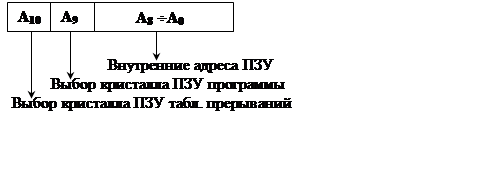

Проектируемое устройство содержит два постоянных запоминающих устройства с электрическим программированием (PROM).

КР556РТ17 (DD3) емкостью 512 байт содержит исполняемую программу и подключено к 9 младшим разрядам системной шины адреса.

Выборка микросхемы происходит по входу ECS при подаче единичного сигнала на адресную линию A9, (M/IO= “0”) в отличие от прочих микросхем, которые выбираются нулевым уровнем сигнала на соответствующей адресной позиции. Сделано это ввиду того, что по сбросу исполнительный адрес равен FFFF0, соответственно при его выставлении на ША все микросхемы (кроме ПЗУ) закрываются и выполняется команда JMP, записанная по указанному адресу в ПЗУ. Таким образом, отпадает необходимость в так называемом “ПЗУ загрузки”.

КМ1608РТ1 емкостью 32 байта подключается к линиям A3,A2,A1,A0 ША (вывод старшего адресного разряда микросхемы заземлен) и содержит, начиная с адреса 0000b, сформированного на этих выводах, четыре байта (40.00.Е0.FF)h, содержащие адрес подпрограммы обработки прерывания FFE40h.

Выбор микросхемы происходит при A10= “0” и M/IO= “0”.

Адресное пространство системы организовано по принципу раздельной адресации, т.е. адресное пространство ввода-вывода отделено от памяти и обращение к памяти или ВУ зависит от состояния вывода M/IO.

|

Рис.2 Распределение адресных линий памяти.

ПЗУ программы имеет 9 внутренних адресных линий и выбирается единицей на линии А9, ПЗУ таблицы прерываний имеет 4 адресных линии и выбирается нулем на А10.

Соответственно диапазон используемых адресов памяти можно представить в следующем виде (указаны только 2 младших байта ША, старшие биты любые):

1. ПЗУ программ – 11111110.00000000¸11111111.11111111b или FE00h¸FFFFh;

2. ПЗУ табл. пр-й – 00000000.00000000¸00000000.00001111b или 0000h¸000Fh;

|

Рис.3 Распределение адресных линий пространства ввода-вывода ВУ

Исходя из этого, и учитывая, что ВУ срабатывает по сигналу “0” на соответствующей адресной позиции, адреса портов ввода/вывода ВУ запишутся в следующем виде (указан только младший байт ША, старшие биты любые):

1. таймер – 11100000¸11100011b или Е0¸Е3h;

2. БР ЦАП – 11010000b или D0h;

3. JK-триггер – 10110000b или B0h;

Нач.адрес Команда Комментарий

FFE06h: MOV AX, FС00h ; инициализация стека

MOV SS, AX ;

MOV AX, 00 ; инициализация указателя стека

MOV SP, AX ;

MOV AL, 24h ; инициализация таймера, см. ниже

OUT E3h ;

MOV AL, 78h ;

OUT E0h ;

MOV CL, 00h ; инициализация исходных данных

MOV BH, 02h ;

MOV DL, 00h ; светодиод выклчен

STI ; разрешение прерывания

HLT ; ожидание прерывания

FFE40h: IN FFh ; cчитывание текущего отсчета с АЦП

MOV BL, AL ;

SUB CL, BL ; CL=CL-BL

Ja M1 ; переход на М1 при CL>BL (см. примечание ниже)

NEG CL ; обращение знака результата

MOV AL, CL ;

DIV BH ; деление AL=AL/BH

MOV AL,80h ;

SUB AL, CL ; вычитаем результат из 80h

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.