В данной работе таймер требуется для генерации импульсов с периодом повторения 0,001с и 1 минута.

Для реализации данных периодов задействованы все три канала. Для реализации периода 0,001 потребуется один канал, а для периода 1 минуты два канала каскадной схемой.

Каналы 0 и2 работают в режиме 2 – импульсного генератора частоты – канал работает как делитель входной частоты FCLK на N. Сразу же после загрузки УС на выходе OUT с частотой FCLK / N устанавливается нулевой сигнал на время одного периода CLK. Режим 2является режимом с автозагрузкой , т.е. после окончания цикла счета CE автоматически перегружается и счет повторяется . Перезагрузка канала новой константы не влияет на текущий счет, новый счет начинается по окончанию предыдущего.

Канал 2 работает в режиме 0 – прерывание от таймера – низкий уровень сигнала на выходе OUT устанавливается сразу же после загрузки УС. Загрузка константы не оказывает влияния на этот выход. Счет разрешается положительным сигналом на выходе GATA. Изменение состояния счетчика/таймера CE осуществляется по срезу сигнала CLK, причем по первому тактовому сигналу происходит загрузка CE константой CR, и только второй тактовый сигнал принимает участие в счете.

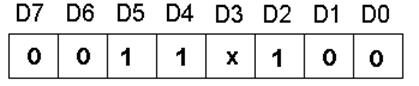

Управляющее слово:

Программирование канал 0 на период 0,001 с:

Поле D7-D6 обозначает, что программируется нулевой канал. Поле D5-D4 устанавливает порядок загрузки/чтения младшего, затем старшего байта данных (константы). Последующие D3-D1 устанавливают режим. Бит D0 устанавливает вид счета и вид загружаемой константы.

Далее загружается константа равная 2500D, константа загружается в двоичном коде т.е. 9C4 H.

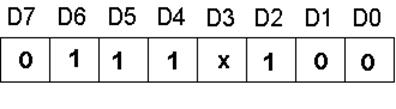

Программирование канал 2 на период 1 минута с использованием канала 1, как дополнительного делителя частоты:

Канал 1

В управляющем слове, по сравнению с каналом 0, изменено D6. Поле D6 совместно с D7 задает канал 1.

Далее загружается константа равная 65535D в двоичном коде, т.е. FFFF. При заданной константе происходит деление поступающей частоты (2,5 МГц) на 65535 и на выходе OUT1 будет частота равная 38 Гц. Сигналы с этого выхода поступают на вход канала 2, проходя через инвертор.

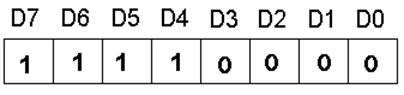

Канал 2

Здесь изменено обозначение канала, т.е. D7 и D6, на код соответствующий каналу 2. Также здесь изменены поля D3 – D1, отвечающие за установления режима.

В этот канал загружается константа равная 2375 D т.е., AAF H.

Нет

Да

|

Нет

![]() Да

Да

|

Нет

Да

|

|||

E008: 000C

0E0F

E3FC: 0008

0E09

E00C: MOV AX, 0000H

MOV DS, AX

MOV ES, AX

MOV SI, AX

MOV DI, AX

MOV SP,AX

MOV AX, 007BH

MOV SS, AX

MOV AL, 11001101B

OUT 4001,AL

MOV AL, 00000110B

OUT 4001,AL

MOV AL, 00001000B

OUT 8001, AL

MOV AL, 00111001B

OUT 8001, AL

MOV AL, 00110100B

OUT 2003,AL

MOV AL, C4H

OUT 2000, AL

MOV AL, 09H

OUT 2000,AL

MOV AL, 01110100B

OUT 2003,AL

MOV AL, FFH

OUT 2001, AL

MOV AL, FFH

OUT 2001, AL

MOV AL, 11110000B

OUT 2003, AL

MOV AL, AFH

OUT 2002, AL

MOV AL, 0A

OUT 2002,AL

HLT

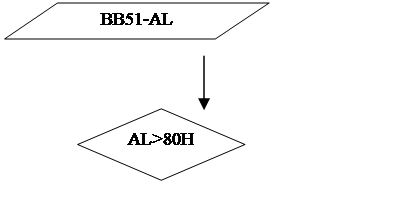

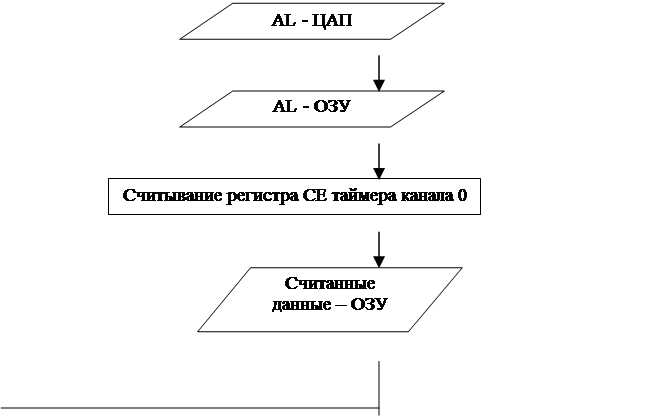

E098: INT AL, 4000H

CMP AL, 80H

JS M1

OUT A000, AL

MOV [SI], AL

INC SI

MOV AL, 00000000B

OUT 2003, AL

IN AL, 2000H

MOV BL, AL

IN AL, 2000H

MOV BH, AL

MOV [SI], BX

ADD SI, 2

M1: HLT

E0FC: MOV AL, 11001101B

OUT 4001, AL

MOV AL, 00100001B

OUT 4001,AL

MOV DI, SI

MOV SI, 0000H

INC SI

M2: MOV AX, [SI]

MOV BX, [SI+3]

SUB AX, BX

CMP BX, 0000H

JZ M3

MOV [SI], AX

ADD SI, 3

JMP M2

M3: MOV AX, 0000H

MOV SI, 0000H

M4: MOV BX, [SI]

ADD SI, 3

CMP BX, 0000H

JZ M5

TEST AX, BX

JNS M4

MOV AX, BX

JMP M4

M5: MOV [DI], AX

ADD DI, 2

MOV AX, FFFFH

MOV SI, 0000H

M6: MOV BX, [SI]

ADD SI, 3

CMP BX, 0000H

JZ M7

TEST AX, BX

JS M6

MOV AX, BX

JMP M6

M7: MOV [DI], AX

MOV BX, [DI-2]

ADD AX, BX

MOV BX, 2

DIV BX

MOV [DI+2], AX

MOV SI, DI

MOV DX, DI

ADD DX, 2

ADD SI, 3

MOV DX, SI

MOV BX, 10

M0: MOV AX, [DI-2]

MOV CX, 3

M8: DIV BX

MOV [SI], DL

INC SI

LOOP M8

CMP AX, 0000H

JZ M9

DIV BX

MOV [SI], DL

M9: INC SI

ADD DI, 2

CMP DX, DI

JNZ M0

SUB SI, 12D

INC SI

MOV AL, 10010000

OUT 8001H, AL

MOV AL, [SI]

OUT 8000, AL

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.